#### **RFNoC 3 Workshop** Part 1

Jonathon Pendlum – Ettus Research Neel Pandeya – Ettus Research

August 2020

#### Schedule

#### Part 1

- RFNoC Framework Overview

- Hands on Demos

- Part 2

- RFNoC FPGA & Software Architecture

- Hands on Computation Engine Development

- Advanced RFNoC Topics

#### PC + Flexible RF Hardware + SDR Framework

0 Q

Research

A National Instruments Company

Ettus

Ó

$\cap$

0

$\cap$

#### PC + Flexible RF Hardware + SDR Framework

GPP: Multi-core + SIMD -- GNU Radio

οŶ

Research

A National Instruments Compan

**Ettus**

6 C

Ó

$\cap$

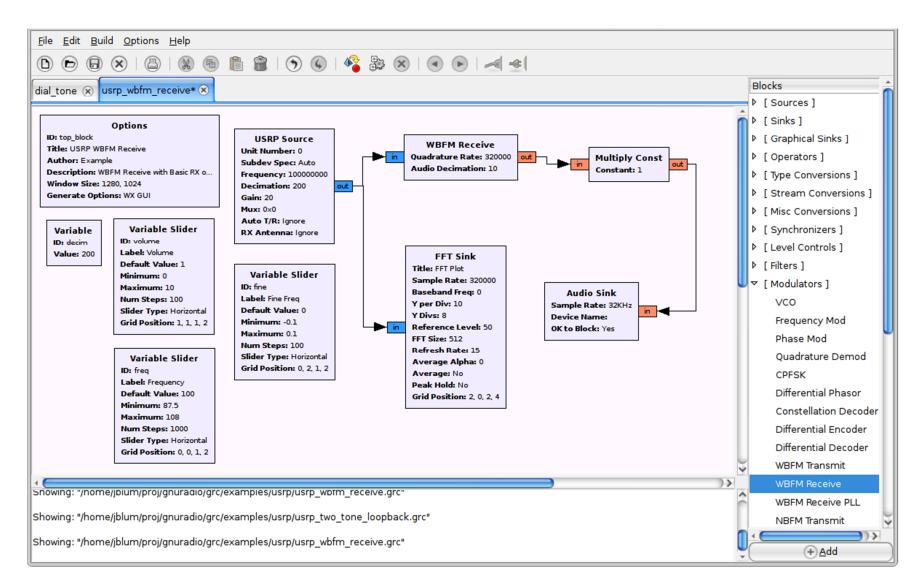

## **GNU Radio**

#### Open source toolkit for developing software radios

90

Research

$\cap$

A National Instruments Co

**Ettus**

Ó

$\bigcirc$

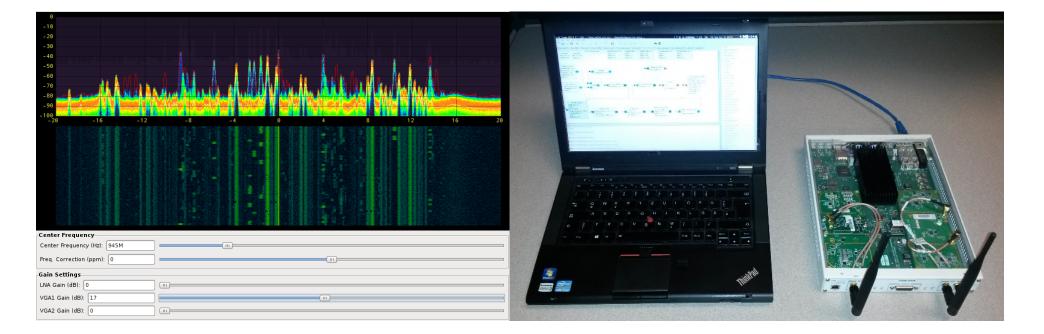

#### PC + Flexible RF Hardware + SDR Framework

GPP: Multi-core + SIMD -- GNU Radio

οŶ

Research

A National Instruments Compan

**Ettus**

6 C

Ó

$\cap$

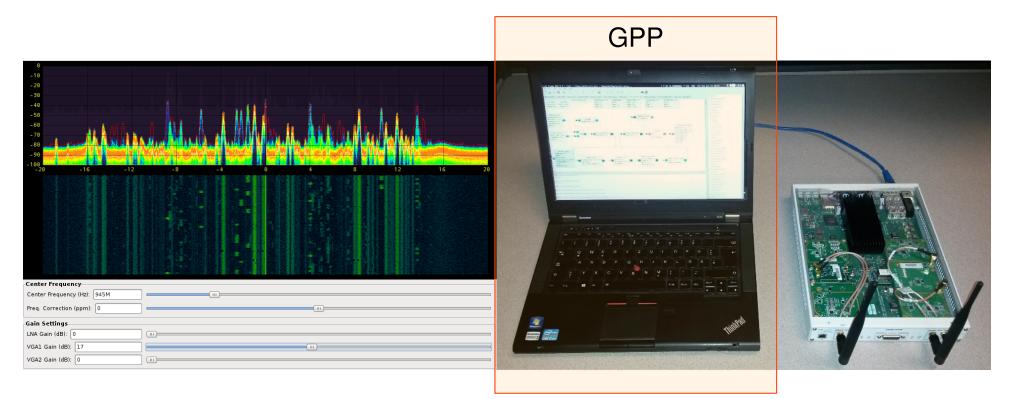

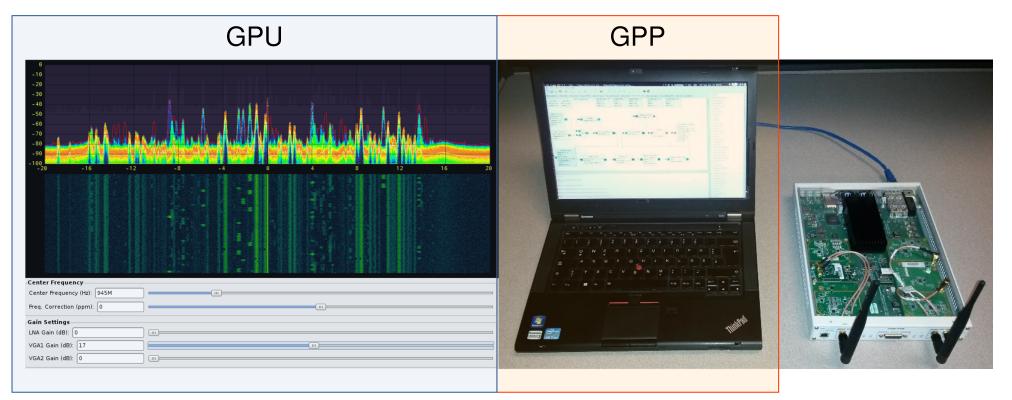

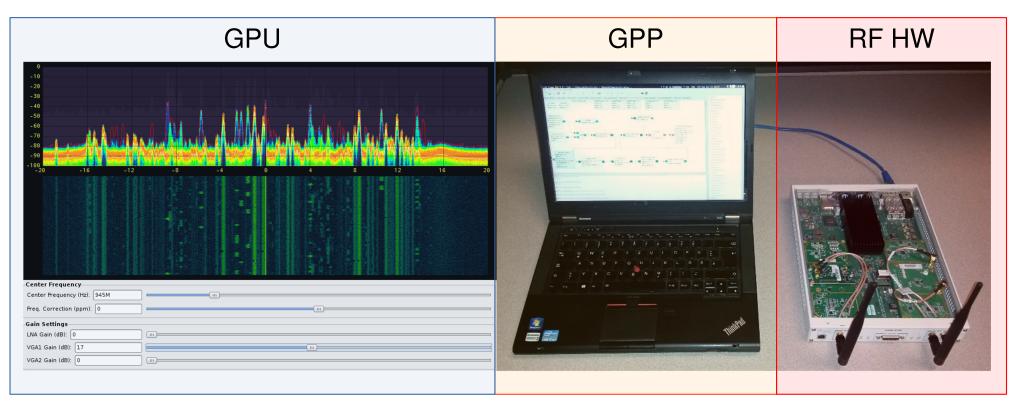

- PC + Flexible RF Hardware + SDR Framework

- GPP: Multi-core + SIMD -- GNU Radio

- GPU: High performance FP -- OpenCL, gr-fosphor

**Ettus**

0 0

Research

A National Instruments Co

- PC + Flexible RF Hardware + SDR Framework

- GPP: Multi-core + SIMD -- GNU Radio

- GPU: High performance FP -- OpenCL, gr-fosphor

- RF HW: Wide bandwidth, large FPGA -- Rate change DSP

**Ettus**

#### **Universal Software Radio Peripheral**

|                     | Gen 1     | Gen 2     | Gen 3 (E310) | Gen 3 (X310) |

|---------------------|-----------|-----------|--------------|--------------|

| FPGA                | Cyclone 1 | Spartan 3 | Zynq         | Kintex 7     |

| Logic Cells         | 12K       | 53K       | 85K          | 406K         |

| Memory              | 26KB      | 252KB     | 560KB        | 3180KB       |

| Multipliers         | NONE!     | 126       | 220          | 1540         |

| Clock Rate          | 64 MHz    | 100 MHz   | 200 MHz      | 250 MHz      |

| <b>RF Bandwidth</b> | 8 MHz     | 50 MHz    | 128 MHz      | 640 MHz      |

| Free Space          | NONE!     | ~50%      | ~60%         | ~75%         |

0 9

Research

$\cap$

A National Instruments Co

Ettus

0

Ó

60

$\cap$

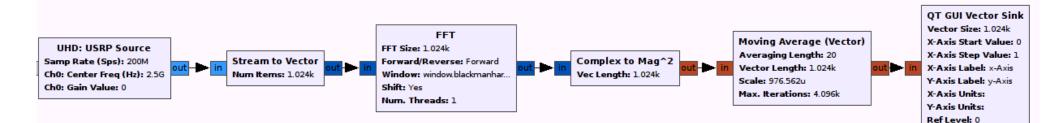

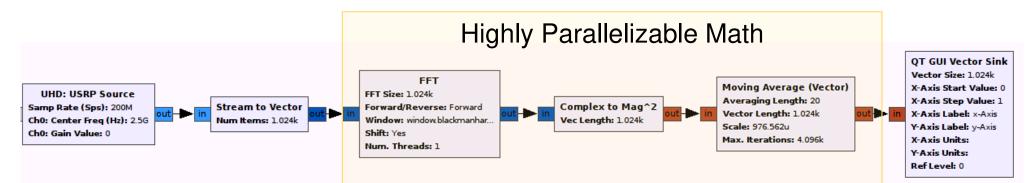

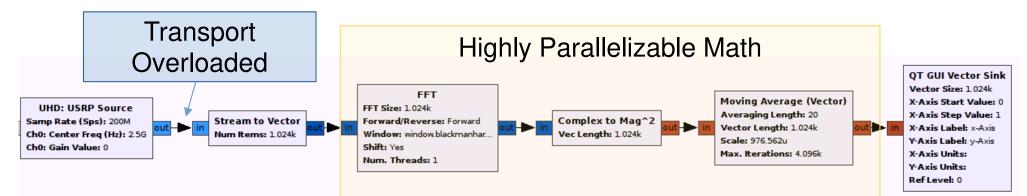

- Massive processing requirements

- Welsh's algorithm for Power Spectrum Estimation

- 1024 FFT + |X|<sup>2</sup> + Moving Average at 200 MSPS

- Massive processing requirements

- Welsh's algorithm for Power Spectrum Estimation

- 1024 FFT + |X|<sup>2</sup> + Moving Average at 200 MSPS

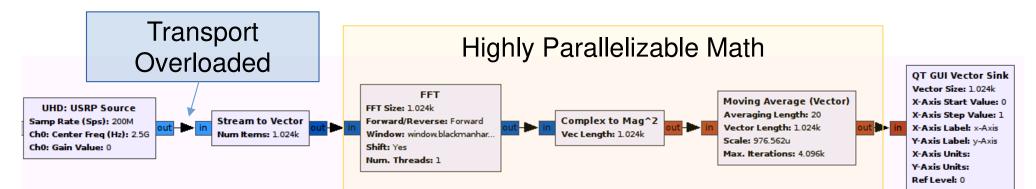

- Massive processing requirements

- Welsh's algorithm for Power Spectrum Estimation

- 1024 FFT + |X|<sup>2</sup> + Moving Average at 200 MSPS

- Overloaded transport

- 200e6 samp/sec \* 32 bits/samp => 6.4 Gb/sec

- Massive processing requirements

- Welsh's algorithm for Power Spectrum Estimation

- 1024 FFT + |X|<sup>2</sup> + Moving Average at 200 MSPS

- Overloaded transport

- 200e6 samp/sec \* 32 bits/samp => 6.4 Gb/sec

- Latency and Determinism

- Ethernet latency, OS scheduling, precise timing

## **Opportunity: Use the FPGA!**

- Everything USRP is open source, available online (code, firmware, schematics)

- Contains big and expensive FPGA!

- Why do customers not use it?

**Ettus**

#### FPGAs: Hard to use... slow to develop

**Ettus**

$\diamond$

Resea

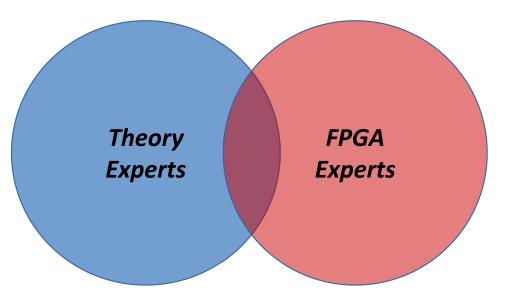

#### **Domain vs FPGA Experts**

- FPGA development is not a requirement of a communications engineering curriculum

- Math in FPGAs is hard

- Complicated system architecture

atmost pure-noise channels. This intuition is clarified more by the following inequality. It is shown in [1] that for any B-DMC W,

$$1 - I(W) \leqslant Z(W) \leqslant \sqrt{1 - I(W)^2} \tag{2}$$

where I(W) is the symmetric capacity of W.

Let  $W^N$  denote the channels that results from N independent copies of W i.e. the channel  $\langle \{0,1\}^N, \mathscr{Y}^N, W^N \rangle$  given by

$$W^N(y_1^N|x_1^N) \stackrel{\text{def}}{=} \prod_{i=1}^N W(y_i|x_i)$$

(3)

where  $x_1^N = (x_1, x_2, \dots, x_N)$  and  $y_1^N = (y_1, y_2, \dots, y_N)$ . Then the *combined* channel  $\langle \{0, 1\}^N, \mathscr{Y}^N, \widetilde{W} \rangle$  is defined with transition probabilities given by

$$\widetilde{W}(y_1^N|u_1^N) \stackrel{\text{def}}{=} W^N(y_1^N|u_1^NG_N) = W^N(y_1^N|u_1^NR_NG^{\otimes n})$$

**Ettus**

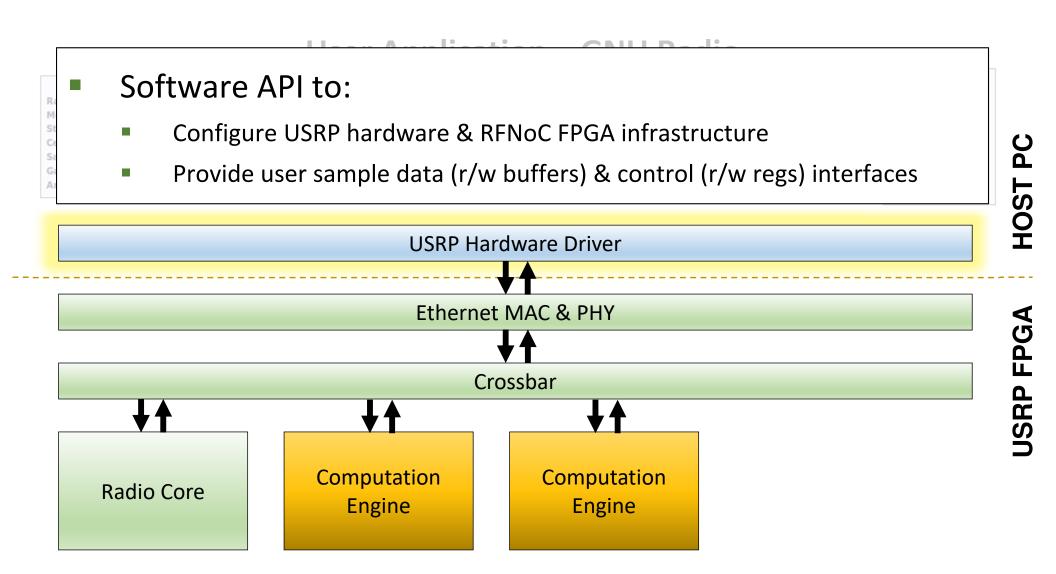

## **RFNoC: RF Network on Chip**

- Ettus

- Make USRP FPGA acceleration more accessible

- Software API + FPGA infrastructure

- Handles FPGA Host communication / dataflow

- Provides users simple software and HDL interfaces

- Infrastructure transparent to user -- reusable code

- Open source

- Fully supported in GNU Radio

- Modularity and composability

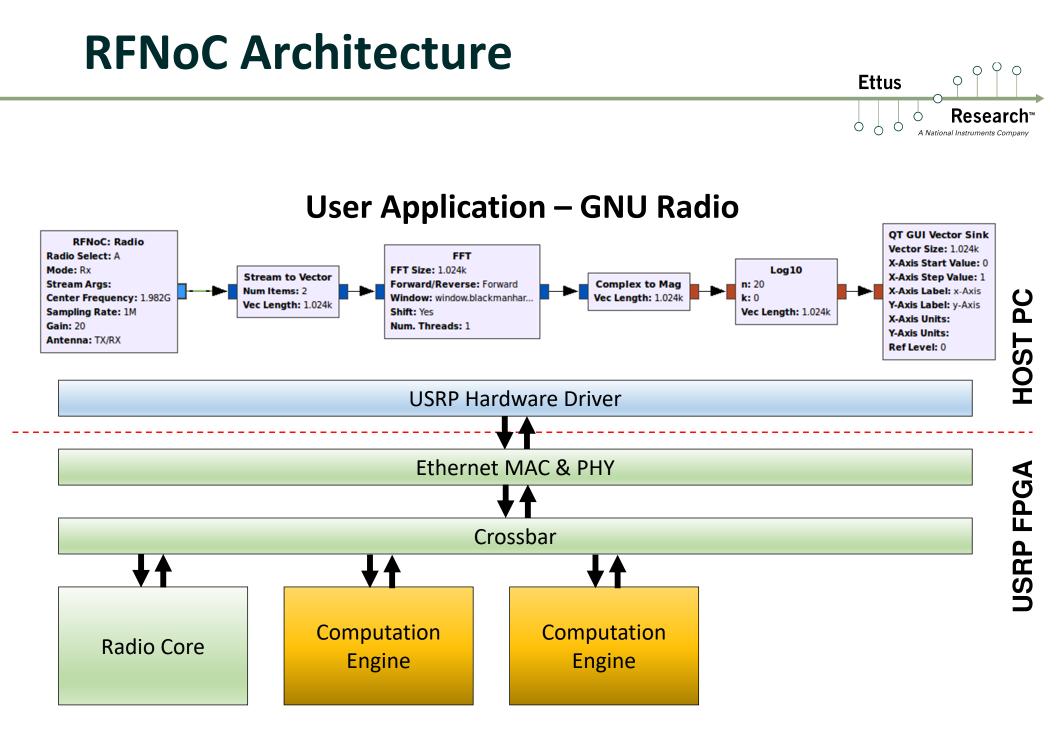

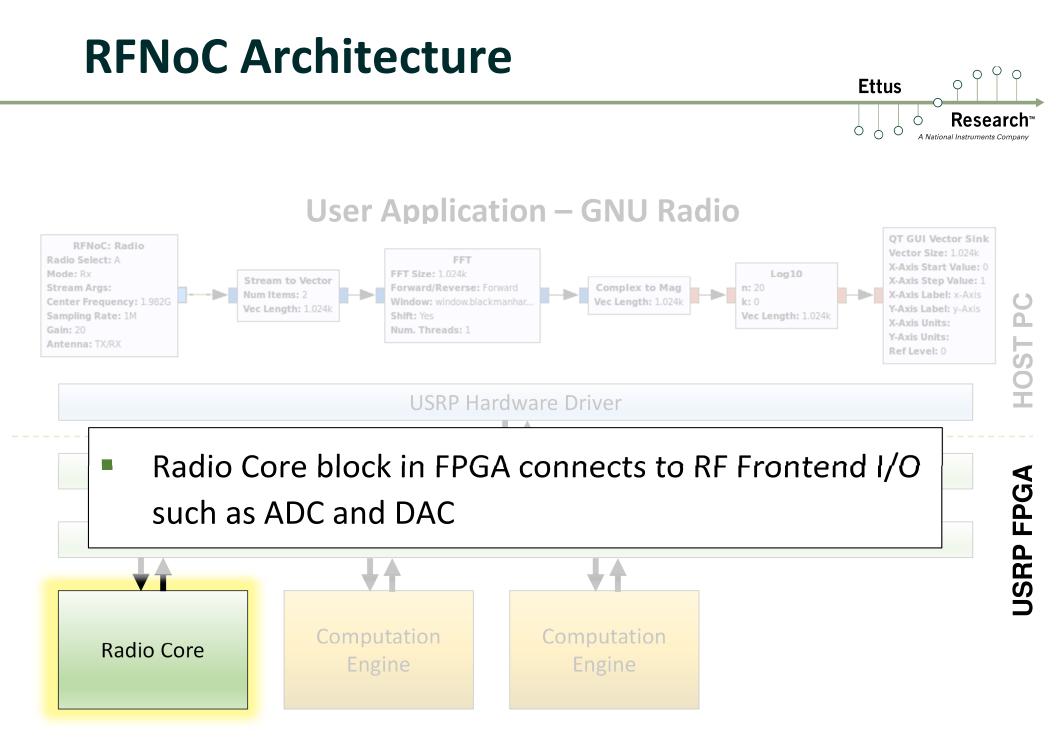

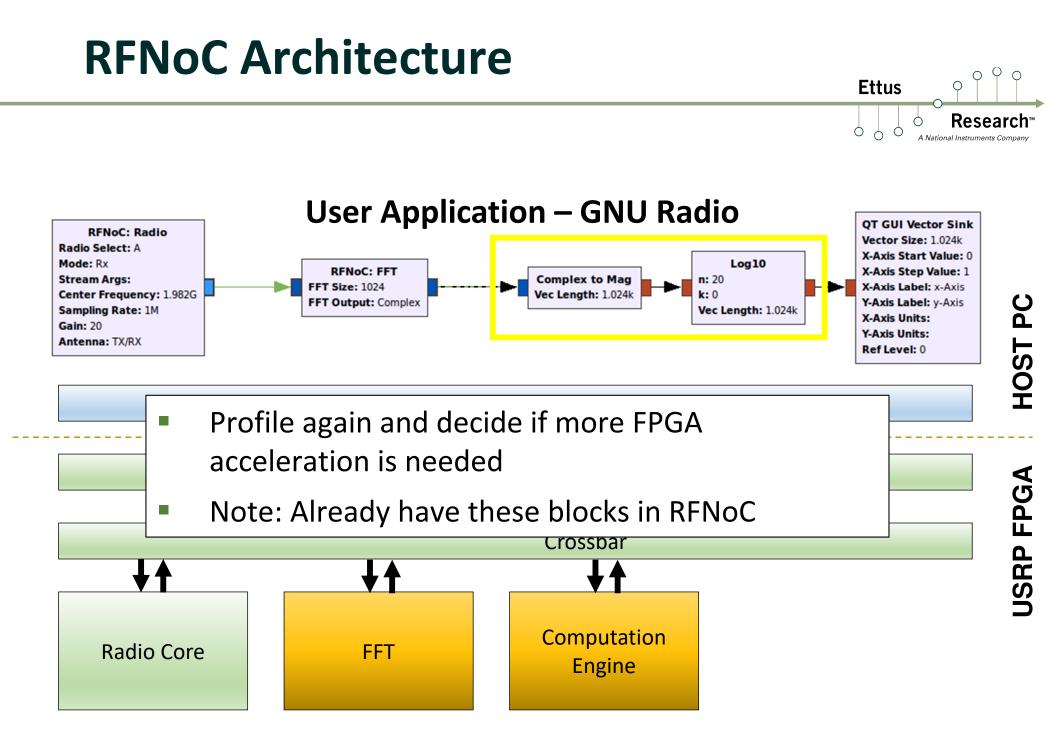

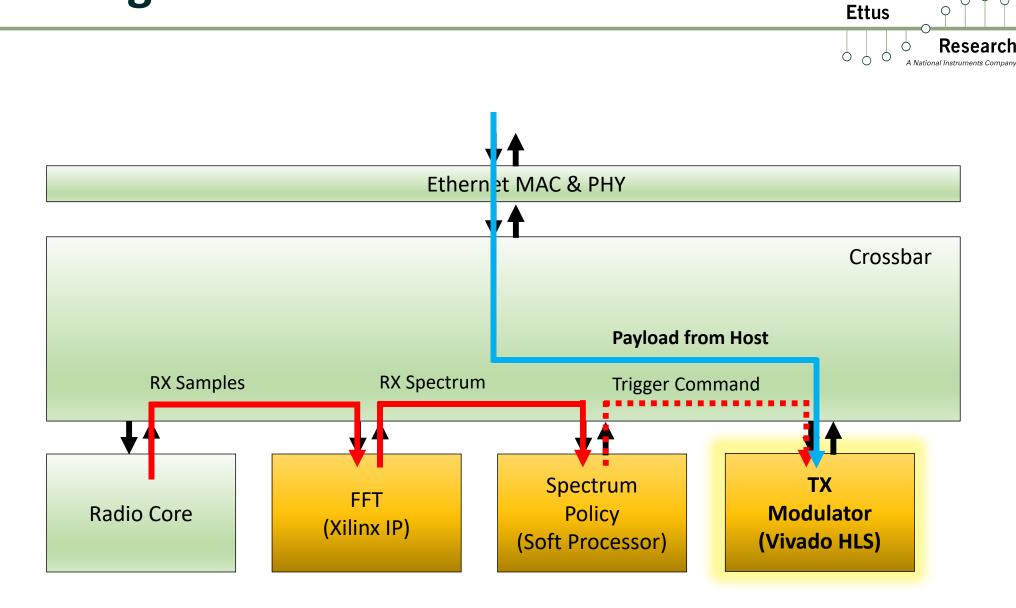

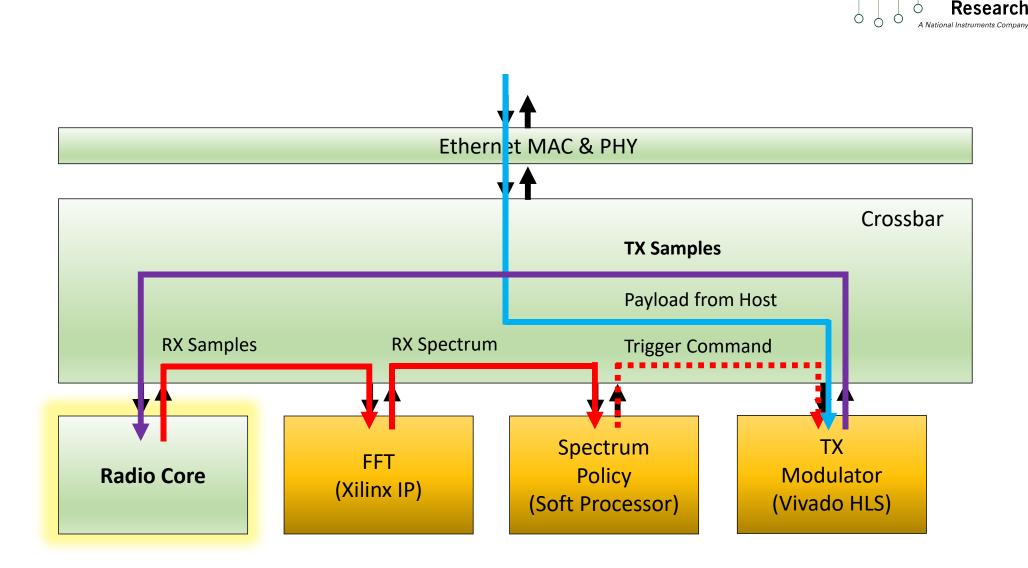

#### **RFNoC Architecture**

**Ettus**

6 C

Ó

Resear

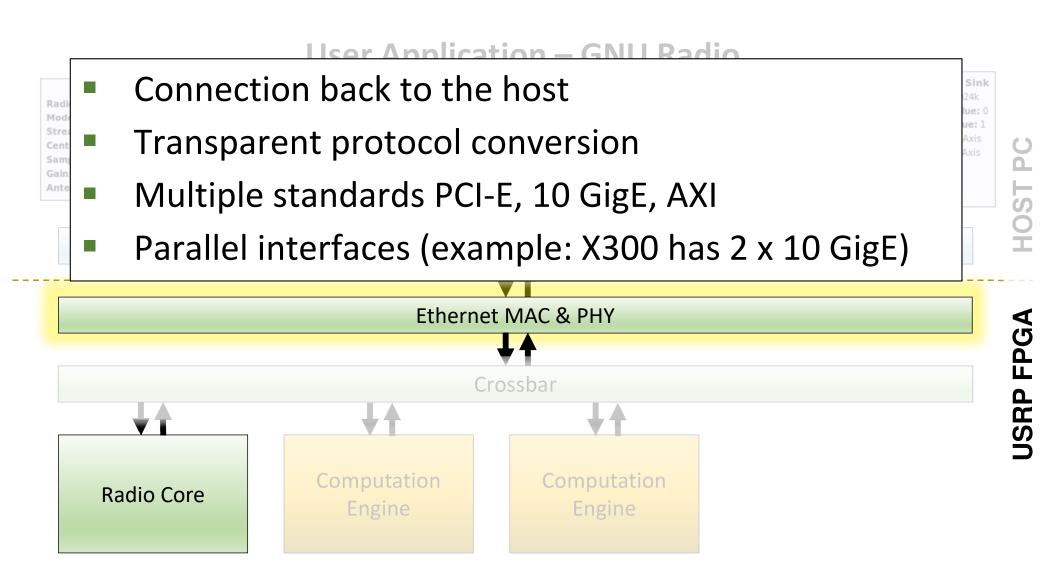

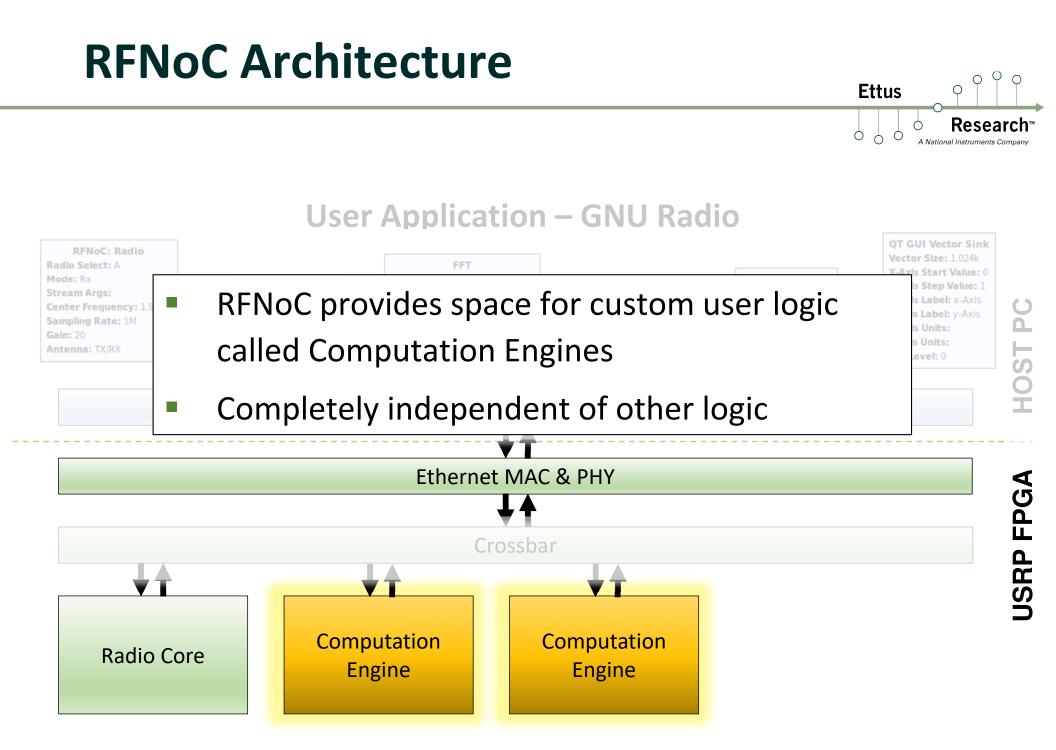

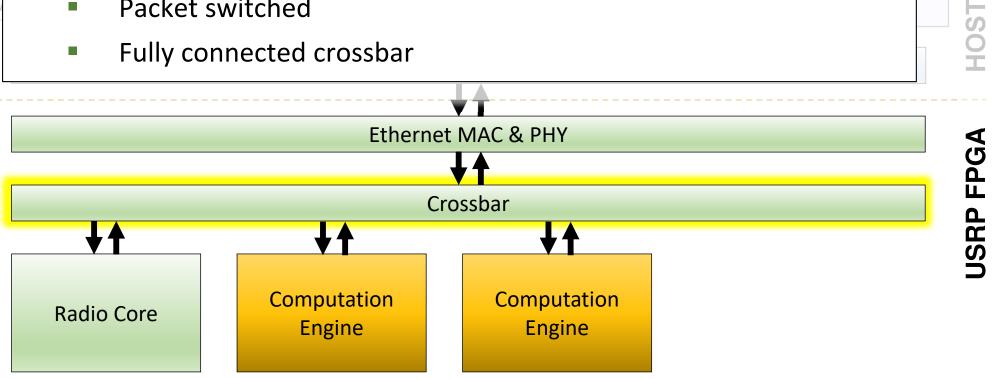

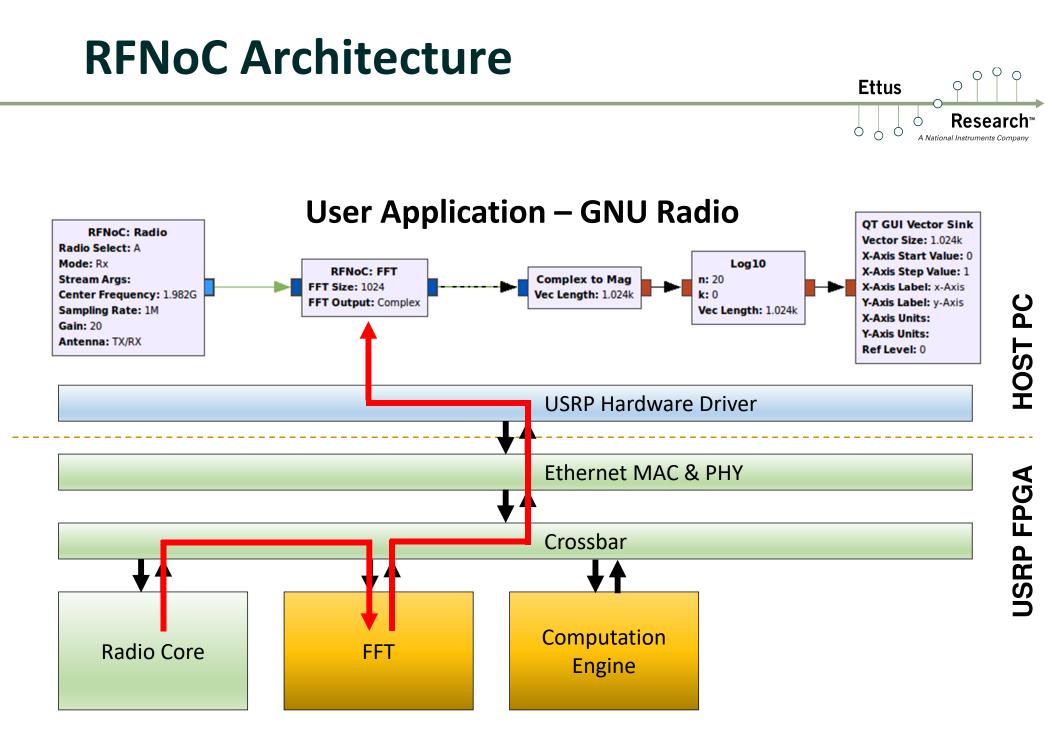

#### **RFNoC** Architecture

#### User Application – GNU Radio

- Crossbar connects Computation Engines, Radio Core, and I/O interfaces (e.g. Ethernet)

- Packet switched

- Fully connected crossbar

**Ettus**

Ć  $\bigcirc$

Ó

Resear

Sink

ue: 0 ie: 1

#### **RFNoC Architecture**

$\cap$

Resea

**Ettus**

6 C

Ó

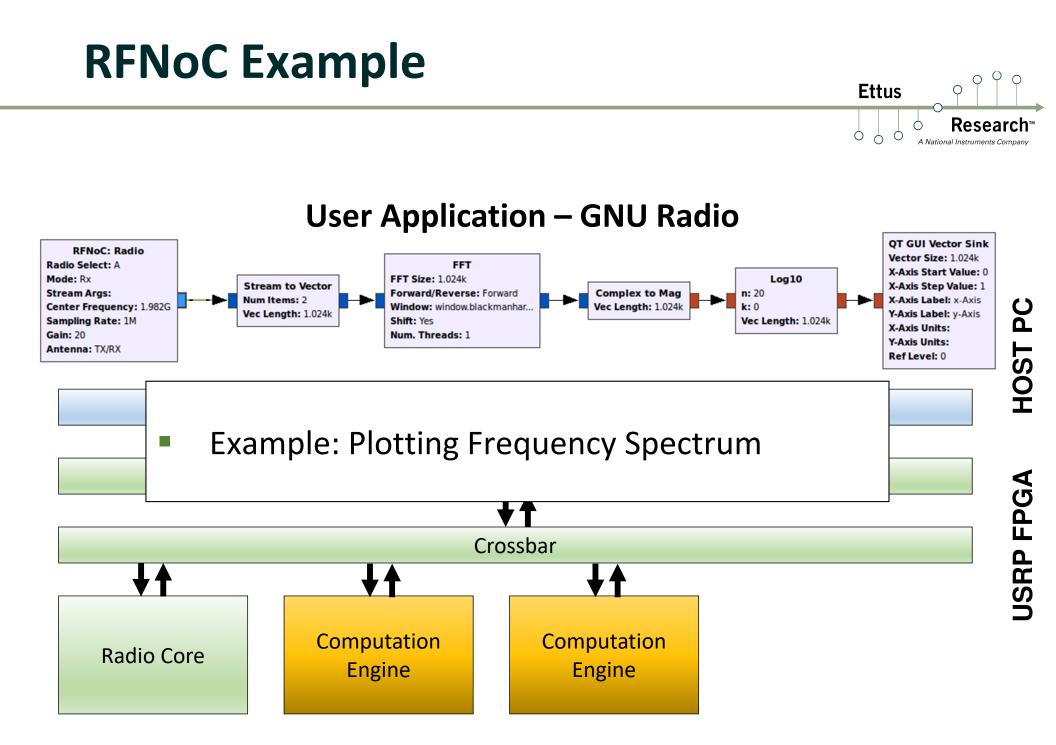

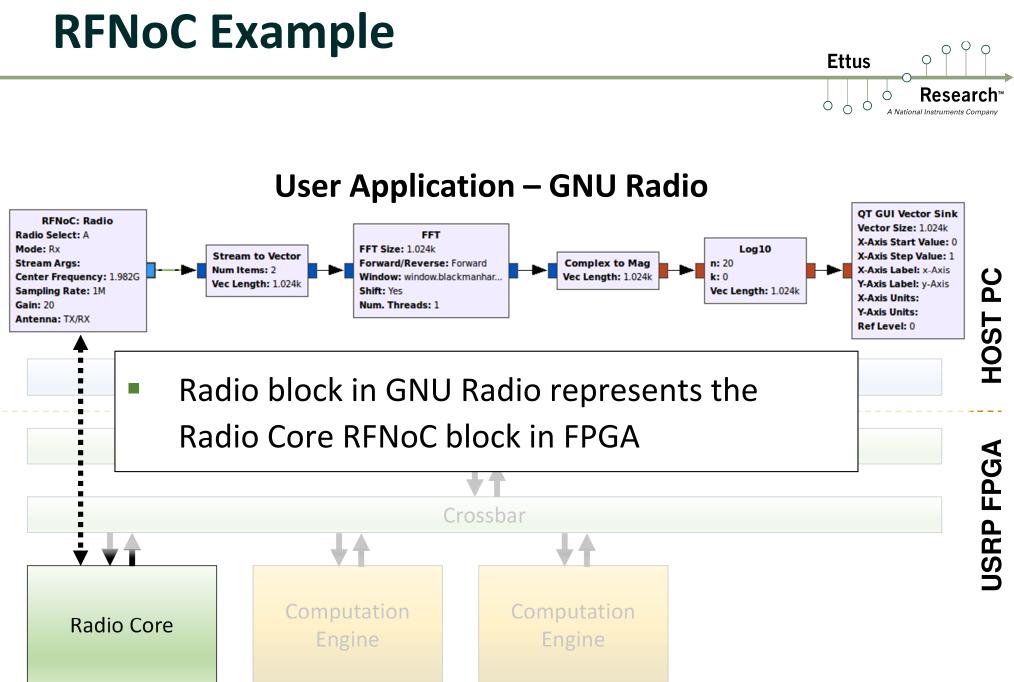

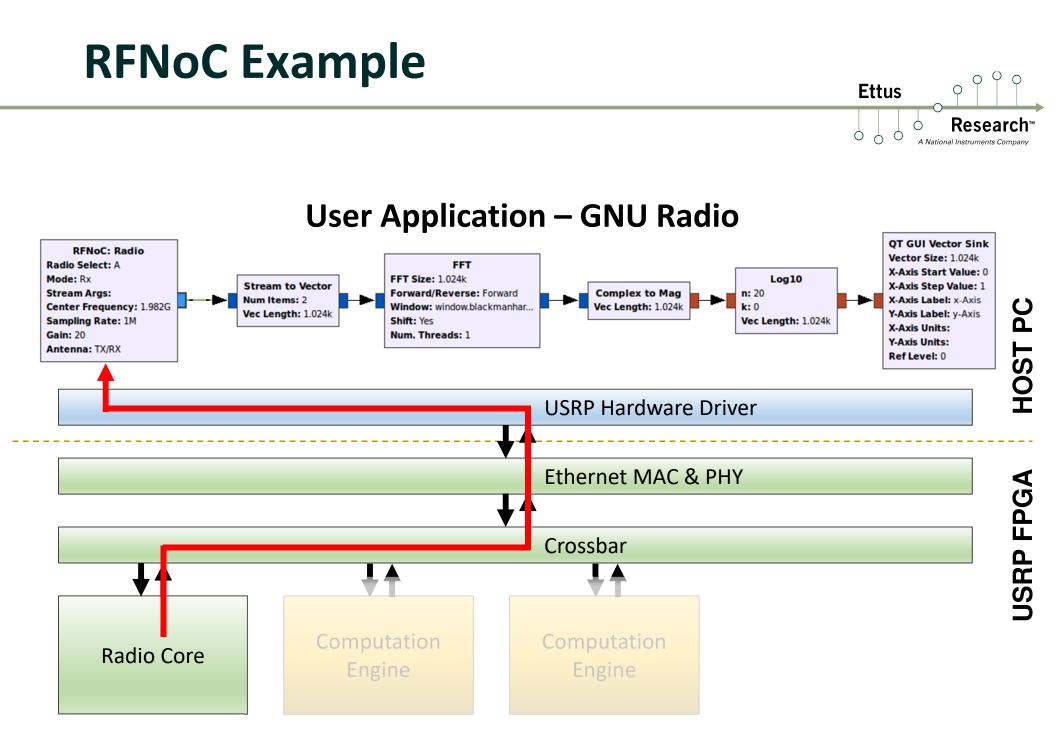

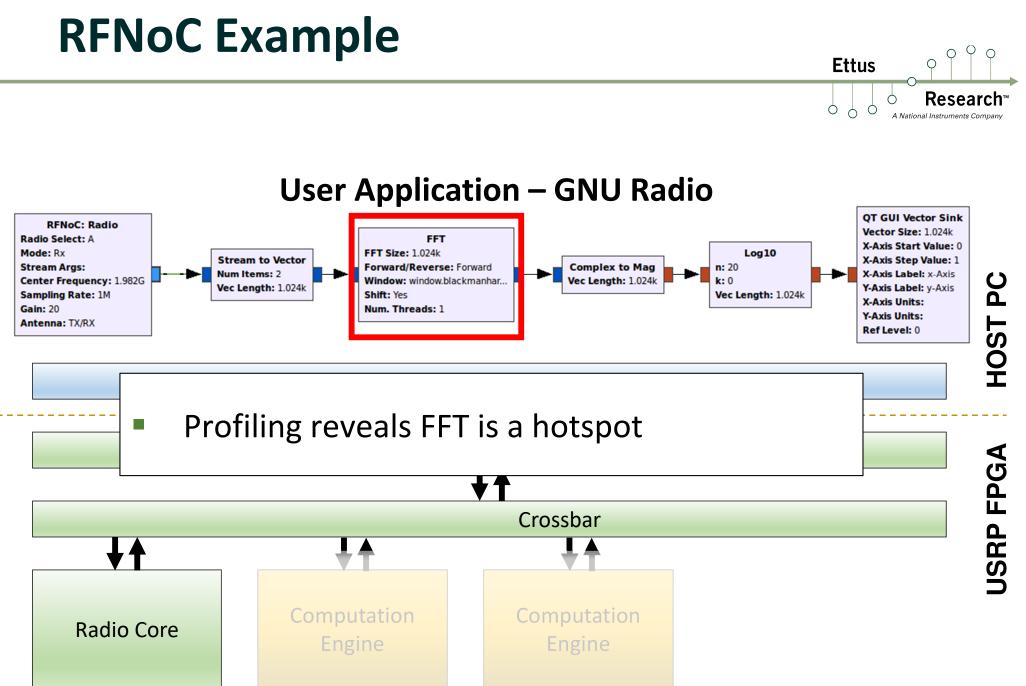

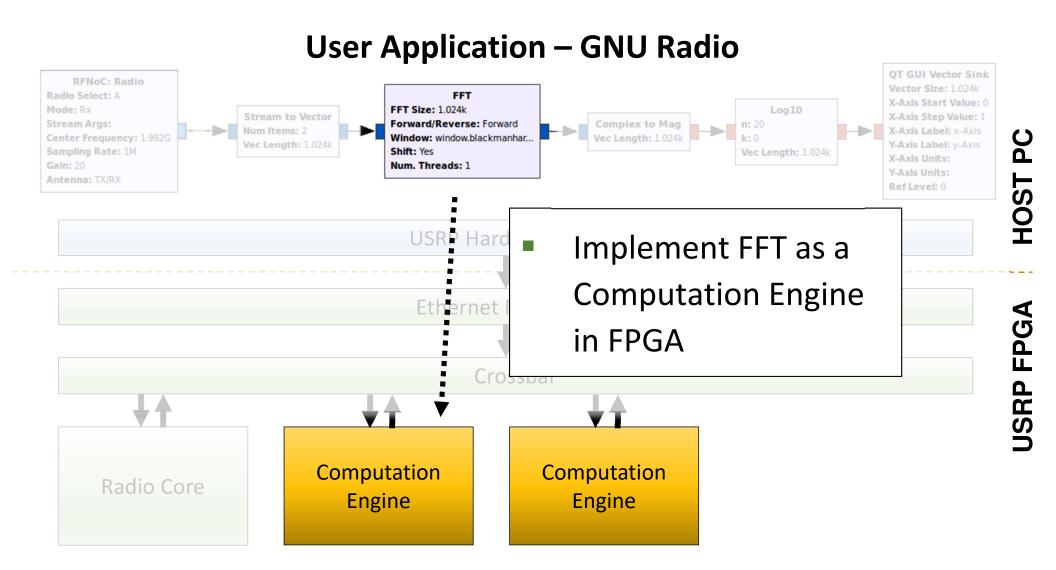

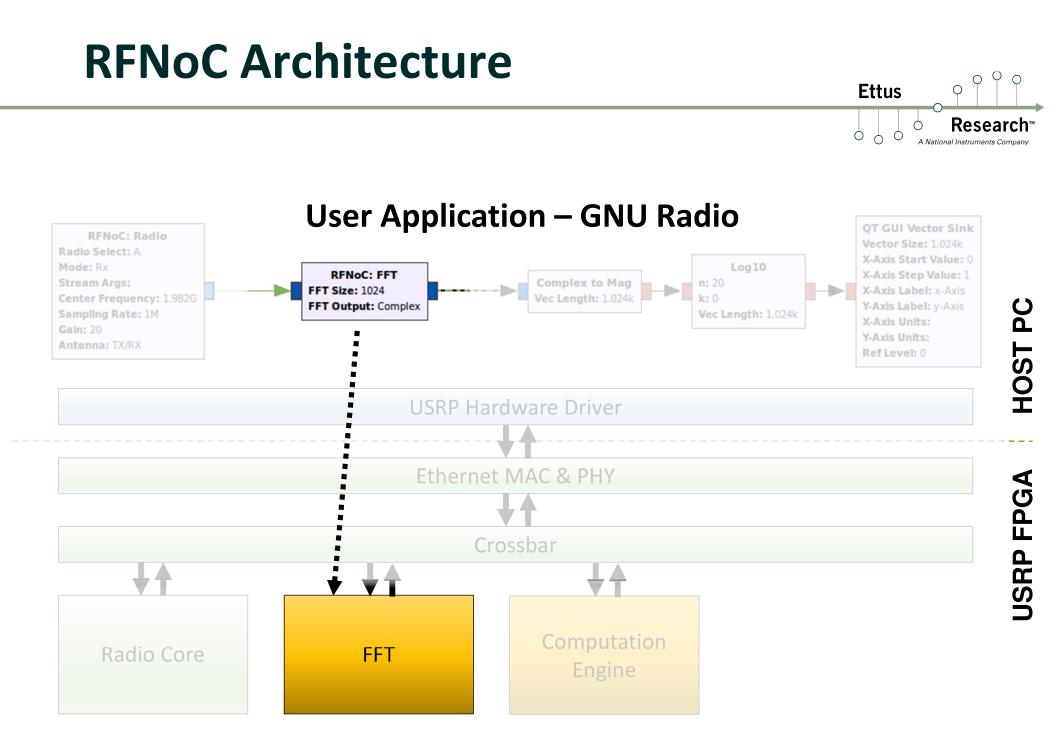

#### **User Application – GNU Radio QT GUI Vector Sink RFNoC: Radio** Vector Size: 1.024k Radio Select: A FFT X-Axis Start Value: 0 Mode: Rx FFT Size: 1.024k Log10 Stream to Vector X-Axis Step Value: 1 Stream Args: Forward/Reverse: Forward **Complex to Mag** n: 20 Num Items: 2 X-Axis Label: x-Axis Center Frequency: 1.982G Window: window.blackmanhar... Vec Length: 1.024k k: 0 Vec Length: 1.024k Y-Axis Label: y-Axis Sampling Rate: 1M Shift: Yes Vec Length: 1.024k X-Axis Units: Gain: 20 Num. Threads: 1 Y-Axis Units: Antenna: TX/RX Ref Level: 0 User application Standalone: C, C++, Python Framework: GNU Radio CLOSSDAL

Computation

Engine

Computation

Engine

**Radio Core**

#### **RFNoC** Architecture

**Ettus** Research Q Ć  $\bigcirc$

A National Instruments Com

PC C HOST

**JSRP FPGA**

# **RFNoC Example**

0 Q

Research

A National Instruments Company

**Ettus**

6 C

Ó

$\cap$

ŶΟ

Q

$\bigcirc$

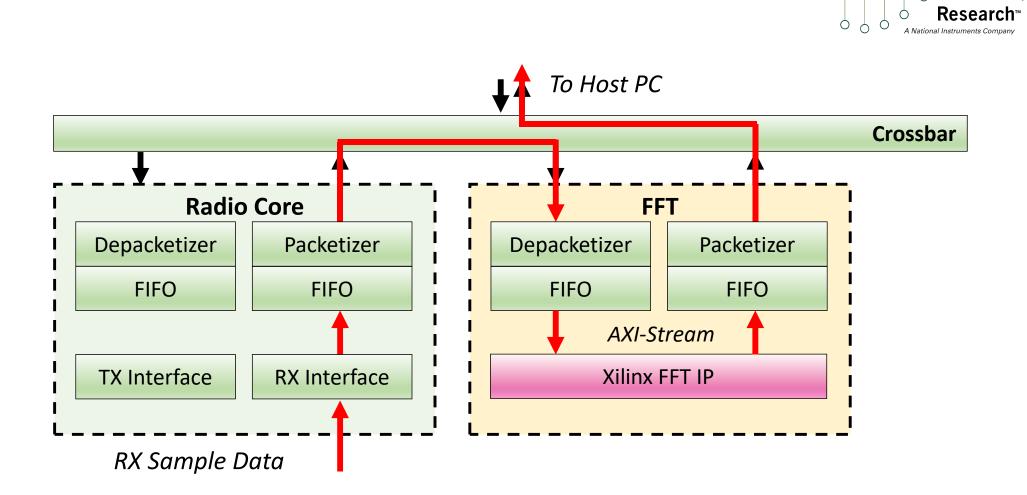

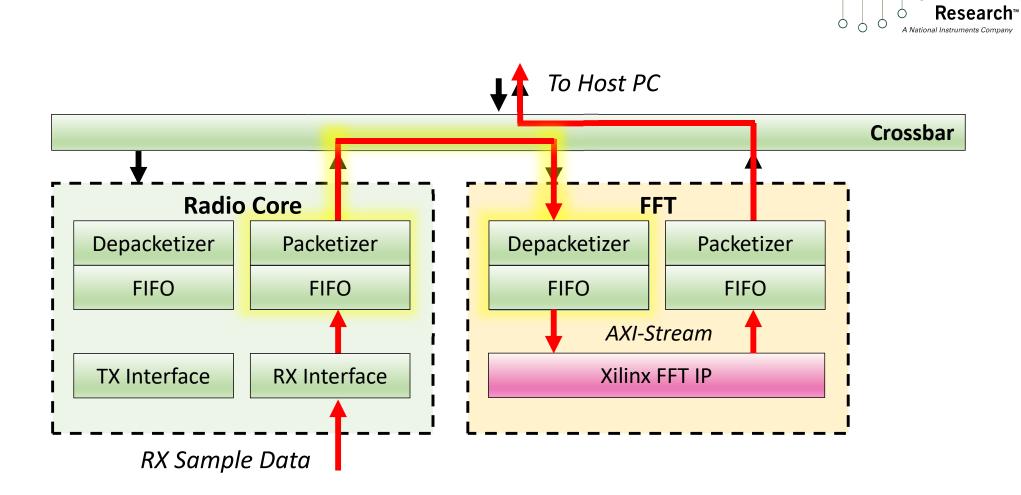

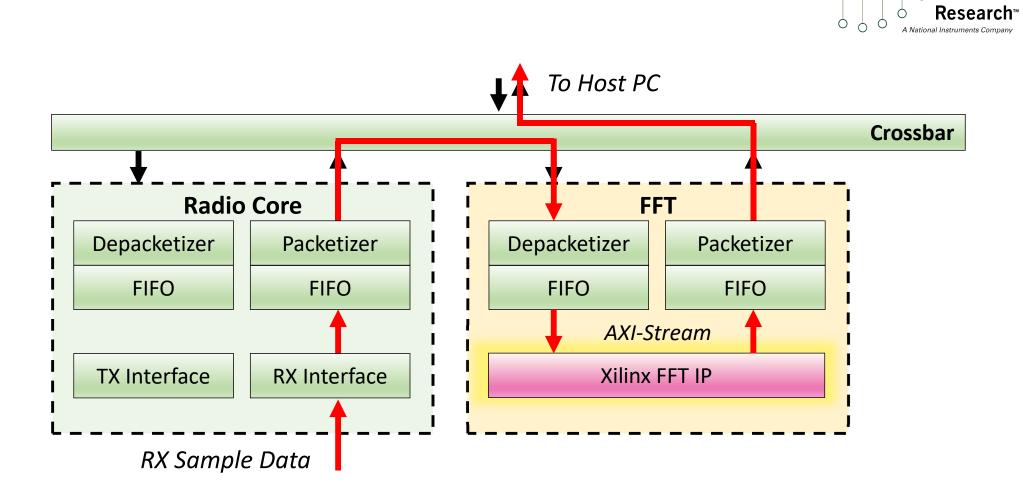

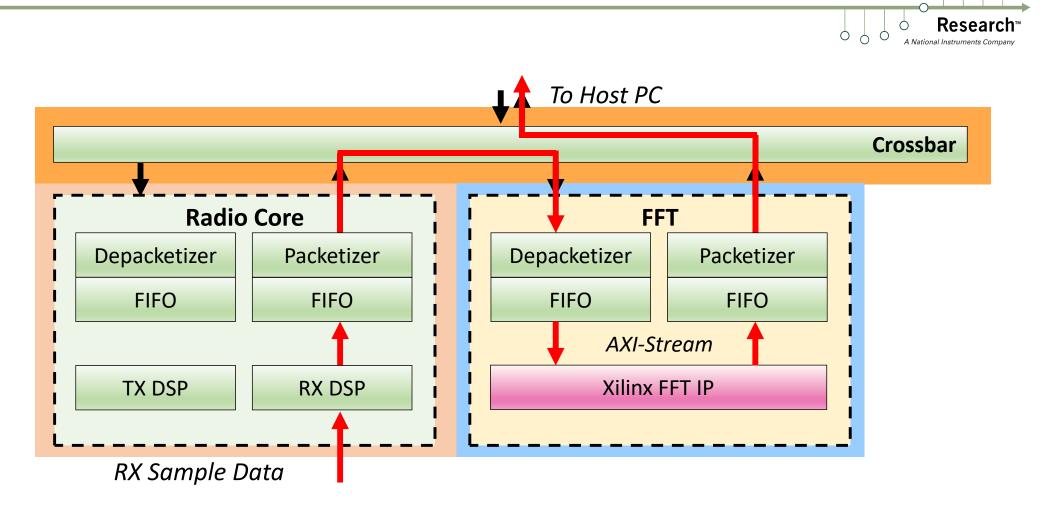

- FIFO to FIFO, packetization, flow control

- Provided by RFNoC infrastructure

0 9

**Ettus**

$\cap$

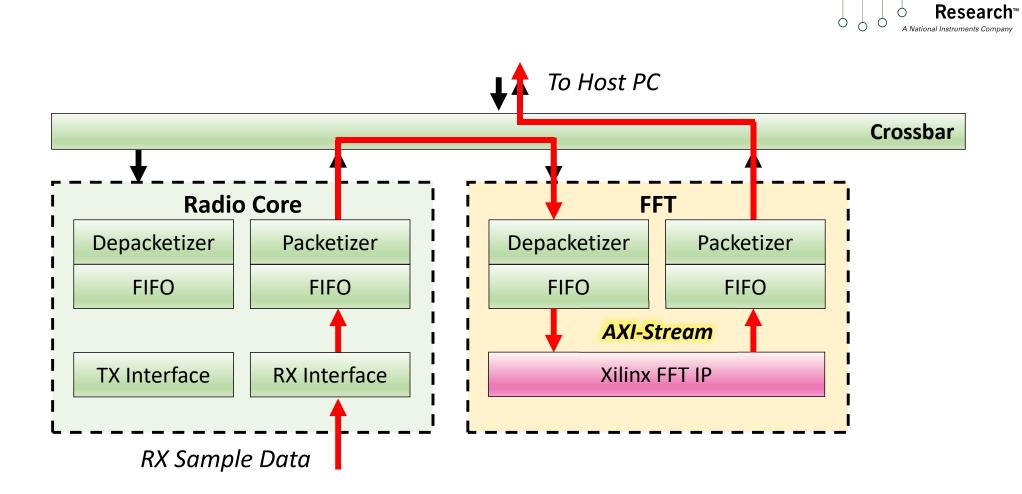

- User interfaces to RFNoC via AXI-Stream

- Industry standard (ARM), easy to use

- Large library of existing IP cores

0 9

**Ettus**

$\bigcirc$

- User writes their own HDL or drops in IP

- Xilinx IP, opencores.org, third party IP

- Vivado HLS, HDL generator software

ΟŶ

- Each block is in their own clock domain

- Improve block throughput, timing

- Interface to Crossbar has clock crossing FIFOs

$\bigcirc$

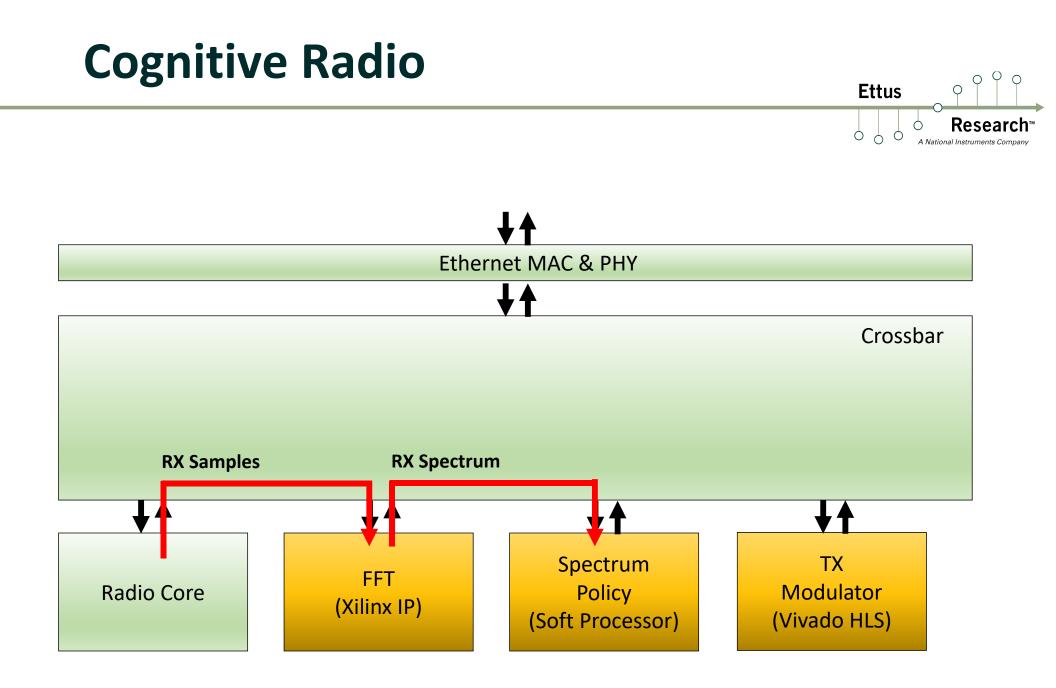

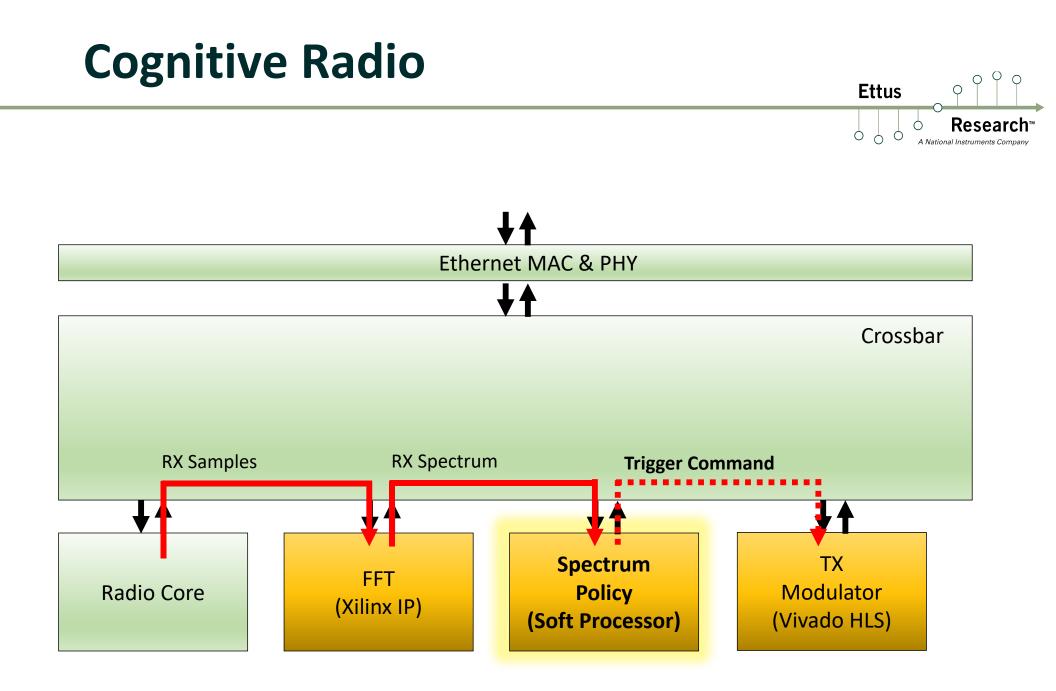

#### **Cognitive Radio**

Q Ο

$\bigcirc$

#### **Cognitive Radio**

0 0

$\bigcirc$

**Ettus**

## **Summary**

- Make FPGA acceleration more accessible on USRP

- Tightly integrated with GNU Radio

- Implemented several interesting CEs

- OFDM, FFT, FIR, Signal Generator, Fosphor

- Portable between all third generation USRPs

- X3x0, E3xx, N3xx

- Completely open source

- kb.ettus.com/RFNoC\_Getting\_Started\_Guides

- After the break: FPGA & Software Development

# Hands on Demos

- Open new terminal and run:

- source ~/rfnoc-workshop/setup\_env.sh

- gnuradio-companion

- rfnoc\_fosphor: Wideband Spectrum Display

- rfnoc\_window\_fft: FFT with selectable window

- rfnoc\_fir: FIR filter with reconfigurable taps

- rfnoc\_ddc: Receive with radio and DDC block

- Flowgraph directory: ~/rfnoc-workshops/src/gr-ettus/examples/