#### RFNoC<sup>™</sup>: RF Network on Chip Martin Braun, Jonathon Pendlum 5/28/2014

## Outline

- Host-based Software Defined Radio

- Current situation

- Goal

- RFNoC

- Architecture overview

- Demo

- Summary

#### **Host-Based SDR – Current Situation**

PC + Flexible RF Hardware + SDR Framework

**Ettus**

- Typical SDR frameworks excel at software reconfigurability & composability

- Less true for available hardware

### **GNU Radio**

Most popular DSP/Streaming Framework in the Free Software Universe

**Ettus**

Ó

- C++/VOLK for fast DSP -- Python for easy scripting

- Graphical Development Tool

- Extensible, many contributions

RFNoC: Not tied to any particular framework

#### **USRP: A White Box?**

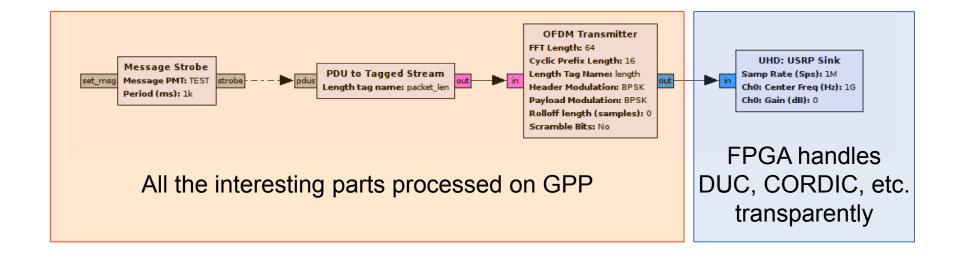

#### Simple OFDM Transmitter Development:

Ettus

Ó

Entire Hardware stack is treated like a reprogrammable ASIC, Features are used as-is

#### **Open the Box!**

Everything USRP is available online (code, schematics)

**Ettus**

Ó

Contains big and expensive FPGA!

#### FPGAs: Hard to use... slow to develop

Ο

Researc

A National Instruments

**Ettus**

0 6 0

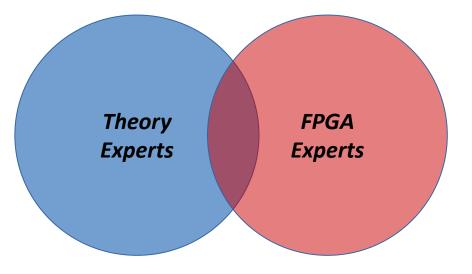

#### **Domain vs FPGA Experts**

## Ettus

- Know Thy Audience!

- FPGA development is not a requirement of a communications engineering curriculum

- Math is hard too

atmost pure-noise channels. This intuition is clarified more by the following inequality. It is shown in [1] that for any B-DMC W,

$$1 - I(W) \le Z(W) \le \sqrt{1 - I(W)^2} \tag{2}$$

where I(W) is the symmetric capacity of W.

Let  $W^N$  denote the channels that results from N independent copies of W i.e. the channel  $\langle \{0,1\}^N, \mathscr{Y}^N, W^N \rangle$  given by

$$W^{N}(y_{1}^{N}|x_{1}^{N}) \stackrel{\text{def}}{=} \prod_{i=1}^{N} W(y_{i}|x_{i})$$

(3)

where  $x_1^N = (x_1, x_2, \dots, x_N)$  and  $y_1^N = (y_1, y_2, \dots, y_N)$ . Then the *combined* channel  $\langle \{0, 1\}^N, \mathscr{Y}^N, \widetilde{W} \rangle$  is defined with transition probabilities given by

$$\widetilde{W}(y_1^N|u_1^N) \stackrel{\text{def}}{=} W^N(y_1^N|u_1^NG_N) = W^N(y_1^N|u_1^NR_NG^{\otimes n})$$

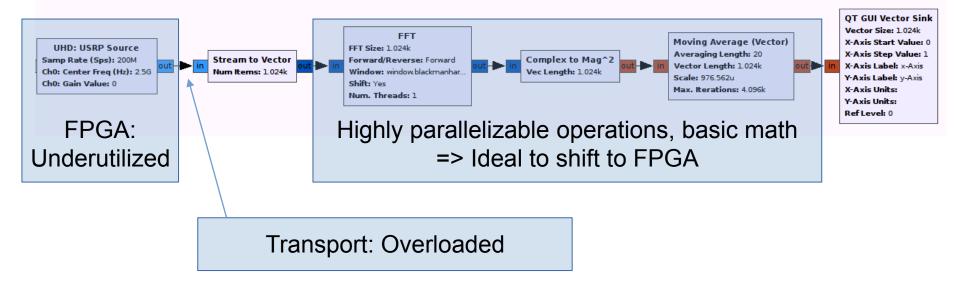

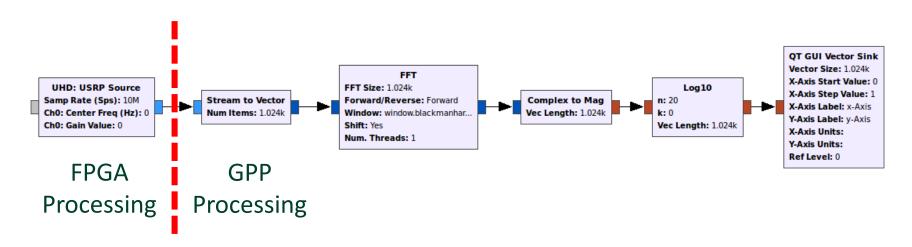

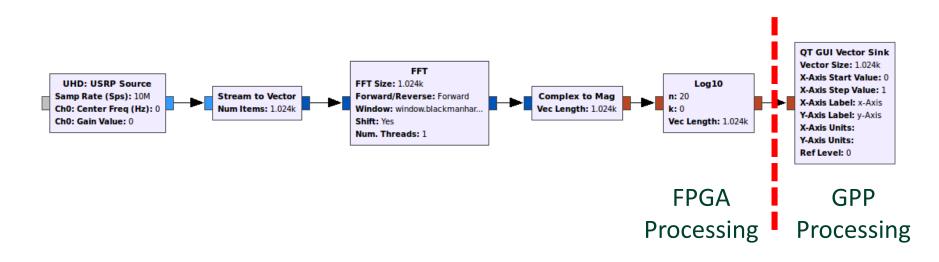

#### **Example: Wideband Spectral Analysis**

#### Simple in Theory: 200 MHz real-time, Welch's Algorithm

Ettus

0 4

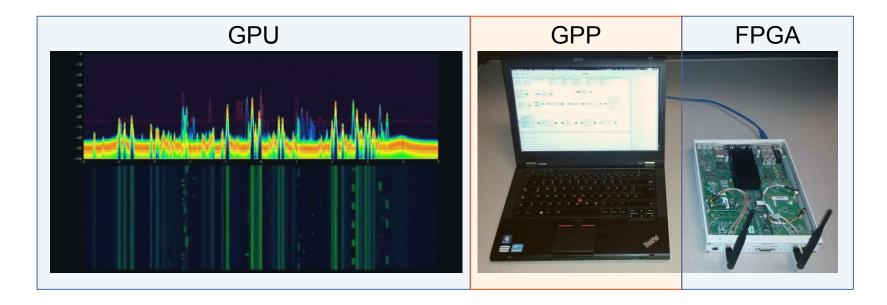

## Goal

- Heterogeneous Processing

- Support composable and modular designs using GPP, FPGA, & beyond

- Maintain ease of use

- Tight integration with popular SDR frameworks

## Goal

- Heterogeneous Processing

- Support composable and modular designs using GPP, FPGA, & beyond

- Maintain ease of use

- Tight integration with popular SDR frameworks

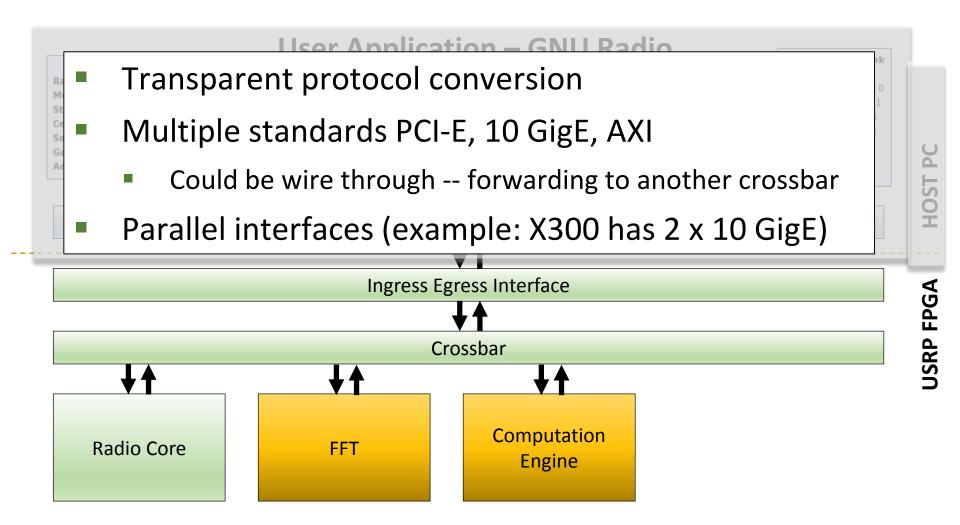

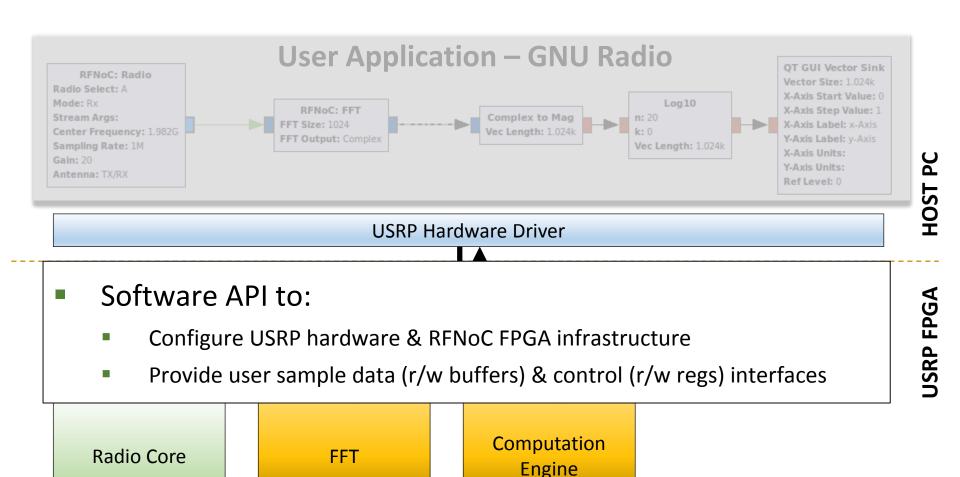

#### **RFNoC: RF Network on Chip**

Ettus Research<sup>TM</sup> A National Instruments Company

- Make FPGA acceleration easier (especially on USRPs)

- Software API + FPGA infrastructure

- Handles FPGA Host communication / dataflow

- Provides user simple software and HDL interfaces

- Scalable design for massive distributed processing

- Fully supported in GNU Radio

**Ettus**

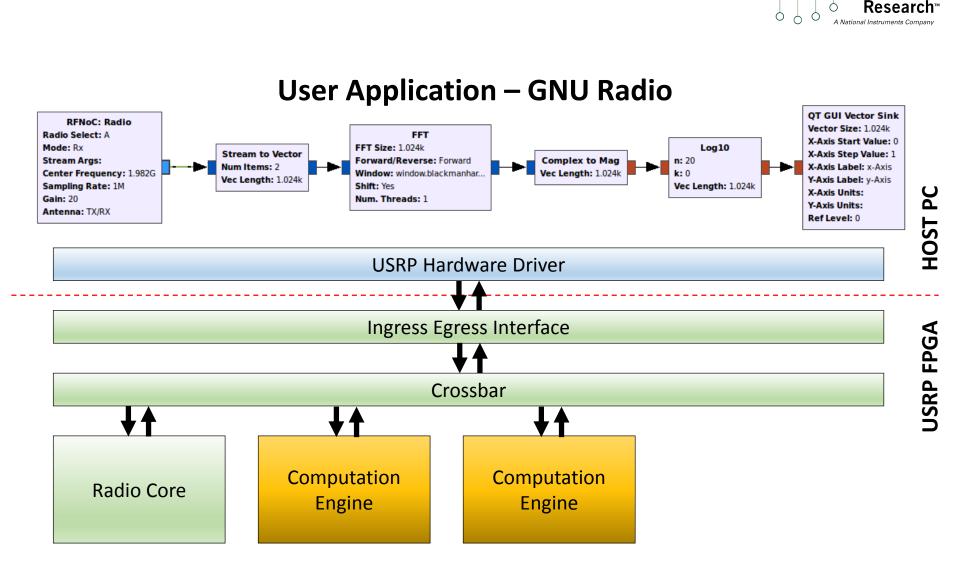

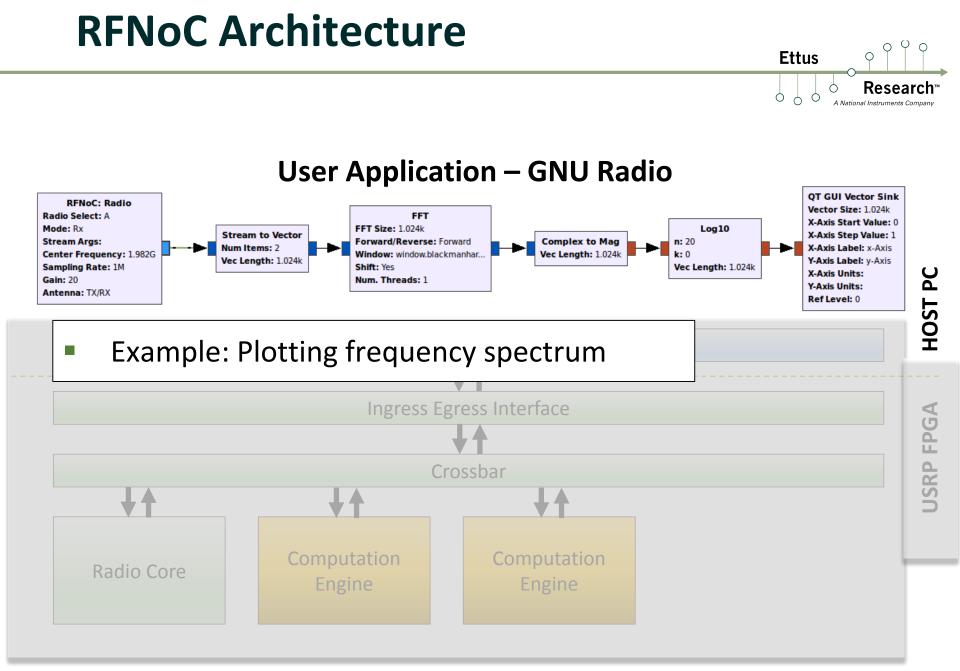

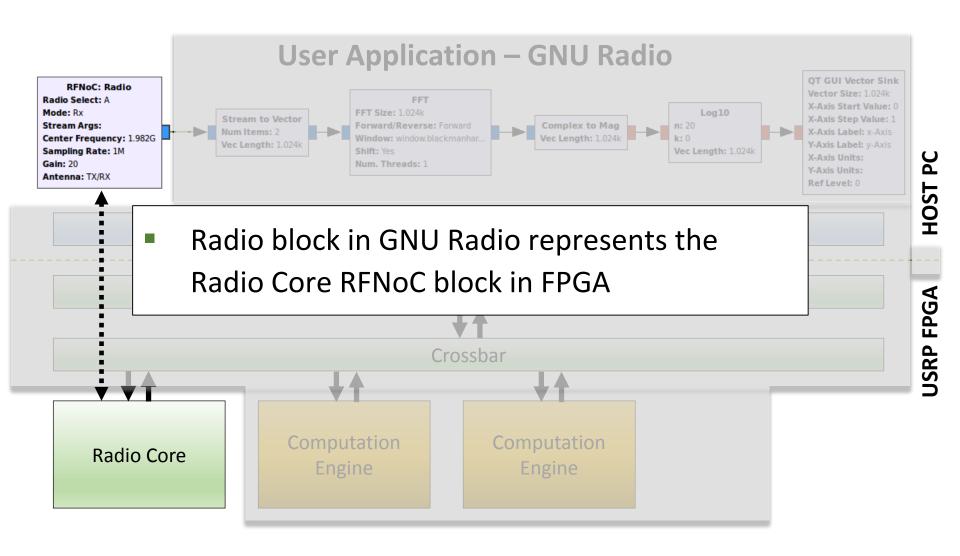

### **RFNoC Architecture**

**Ettus** Resear A National Instruments

Ó

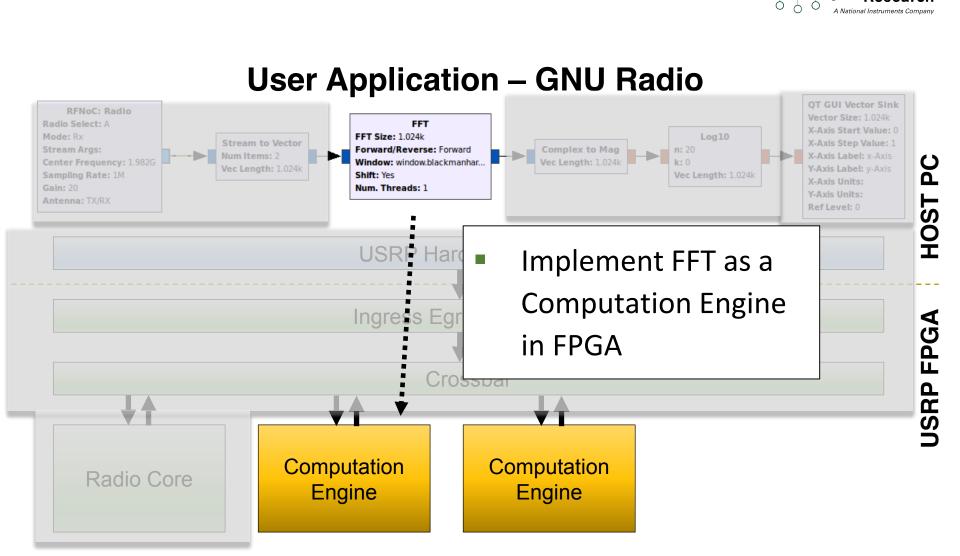

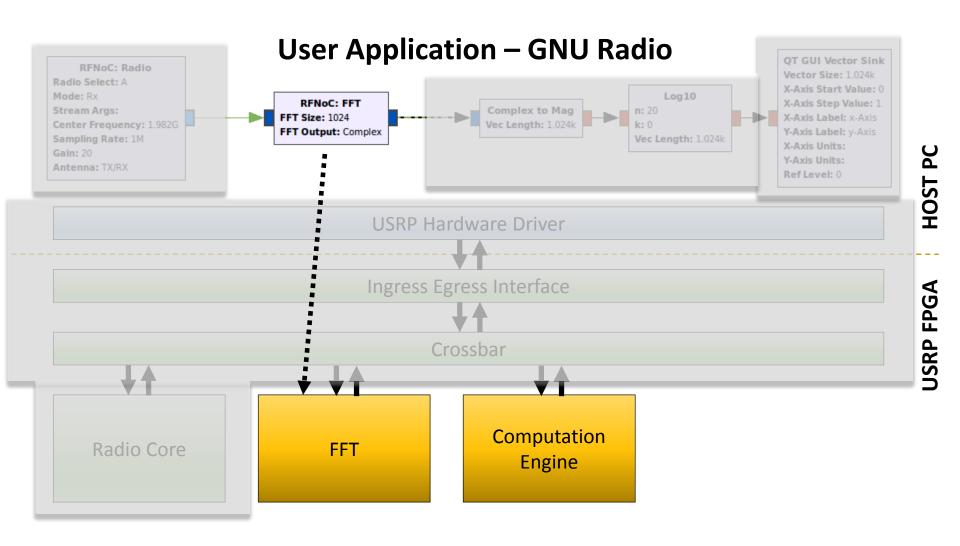

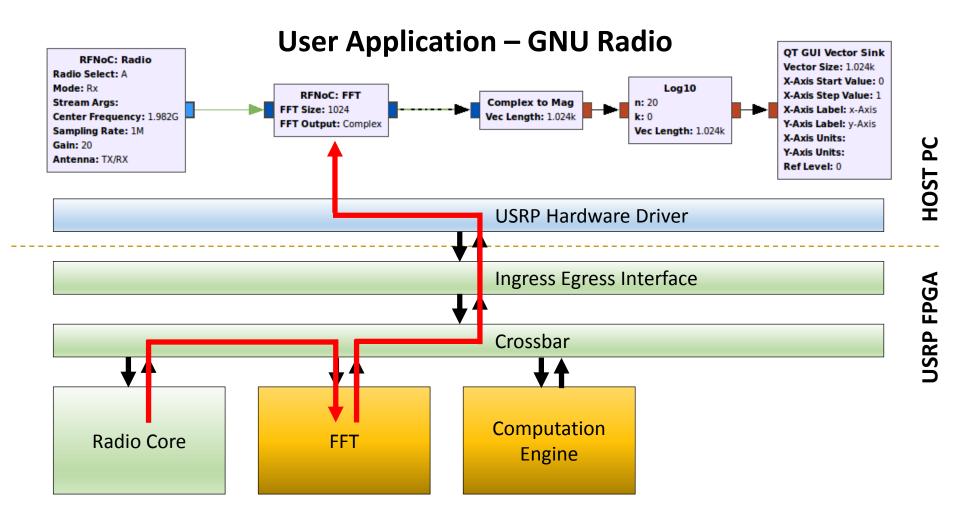

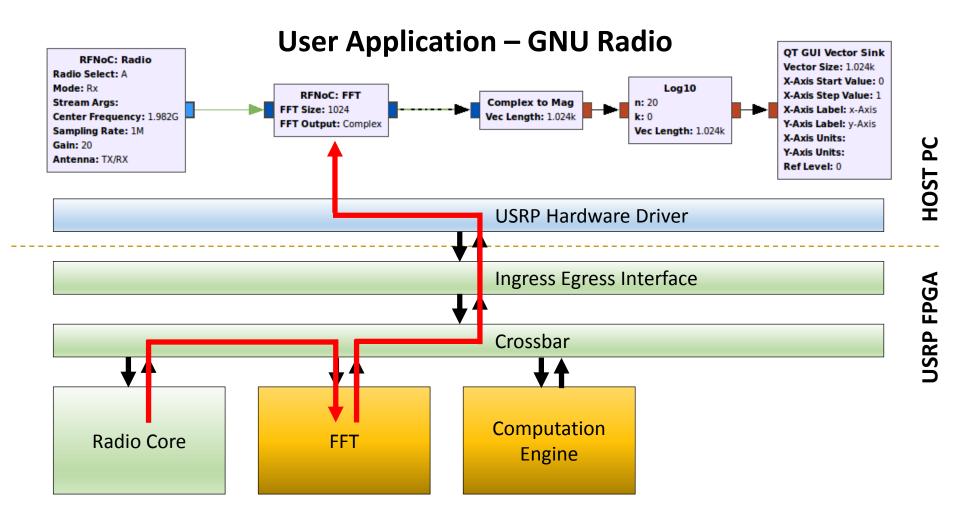

#### **User Application – GNU Radio**

**Ettus**

Ó

Resea

A National Instruments

**Ettus** Resear A National Instruments (

Ó

**Ettus** Resear A National Instruments (

Ó

**Ettus**

Researc

Ο

**Ettus**

0 4

Research

A National Instruments Co

0 9

Research

$\bigcirc$

A National Instruments Co

**Ettus**

Ó

$\cap$

60

0

**Ettus**

Ó

Researc

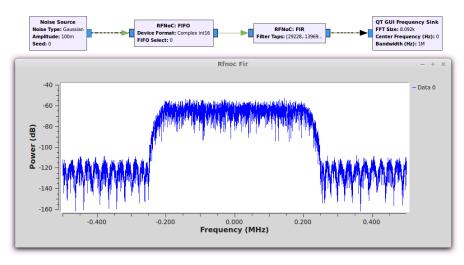

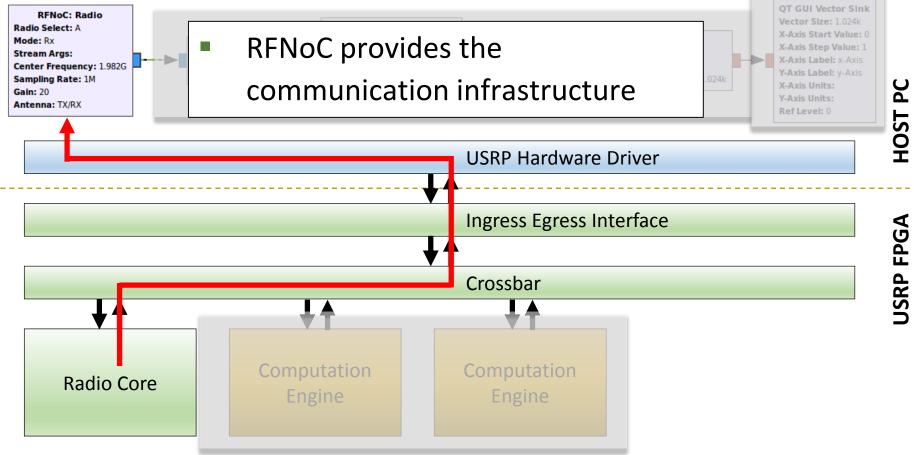

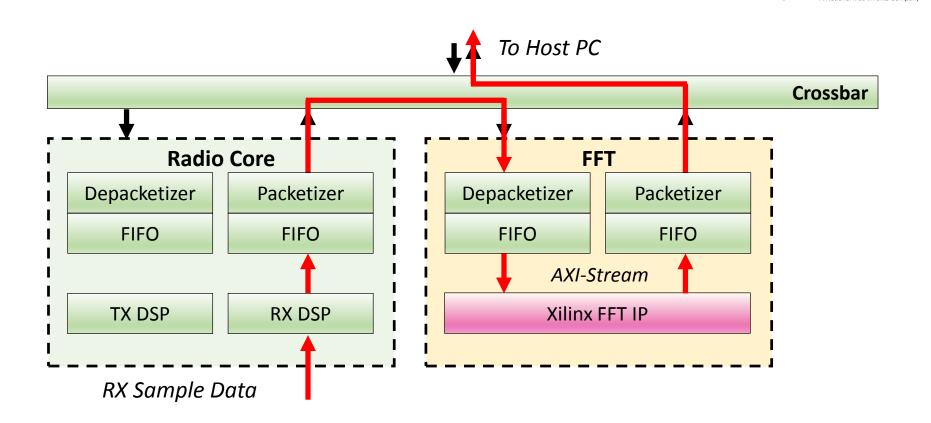

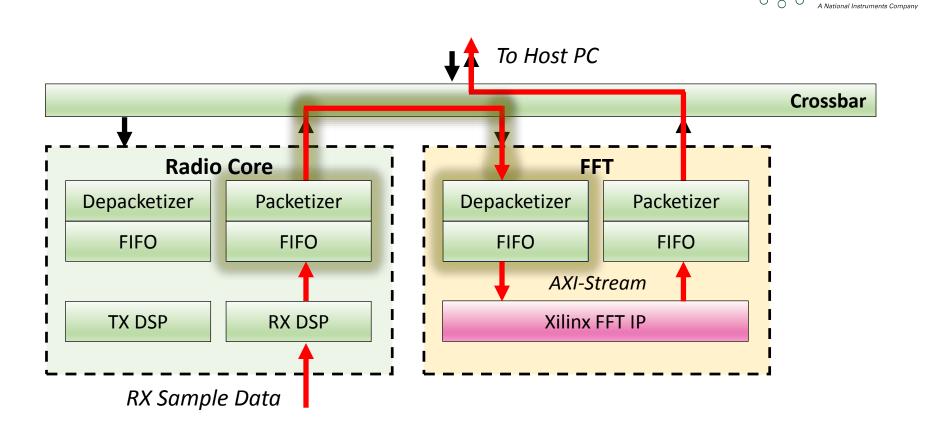

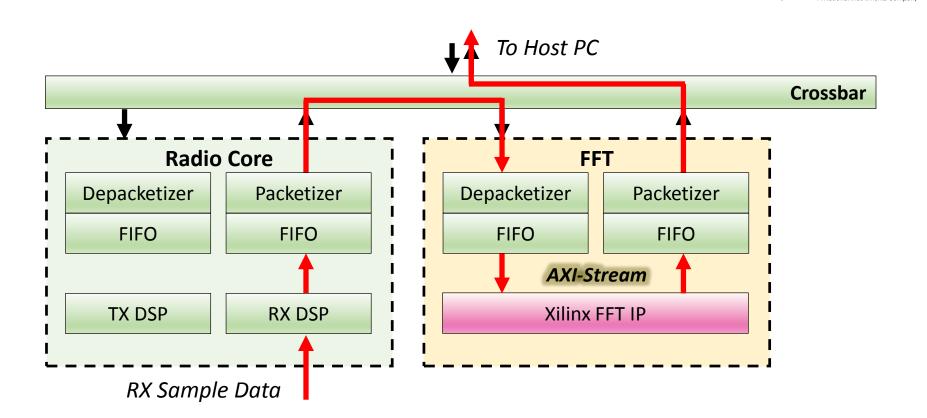

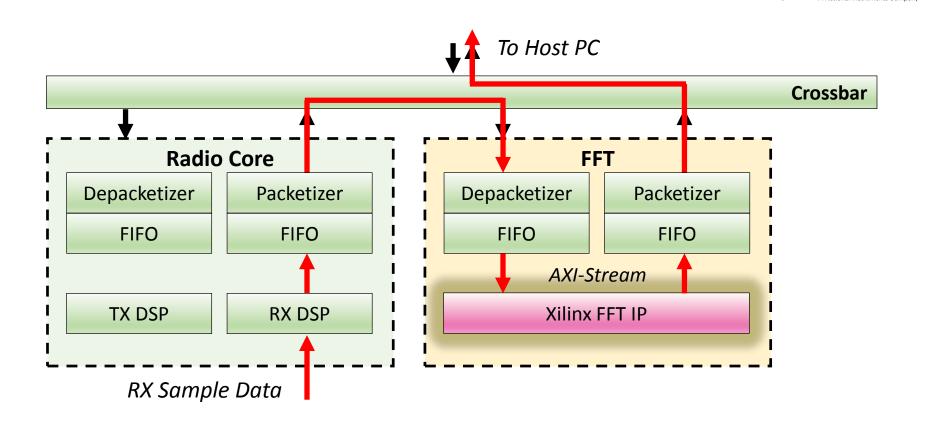

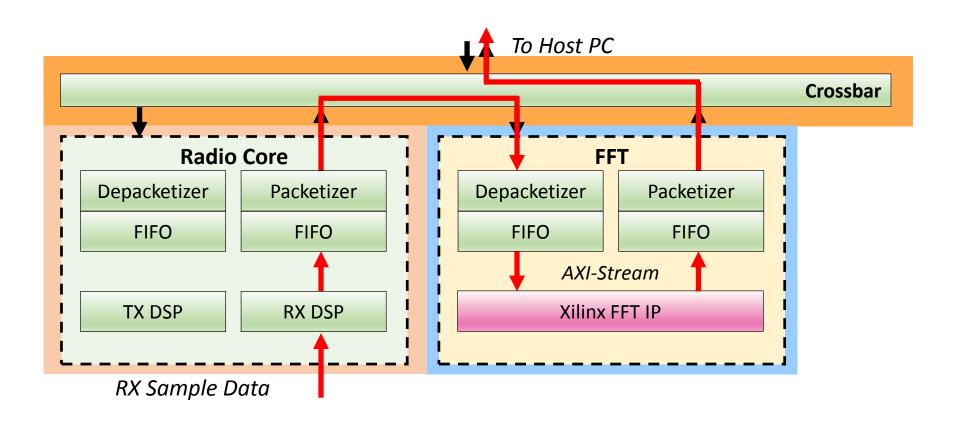

- FIFO to FIFO, packetization, flow control

- Provided by RFNoC infrastructure

**Ettus**

Researd

A National Instruments

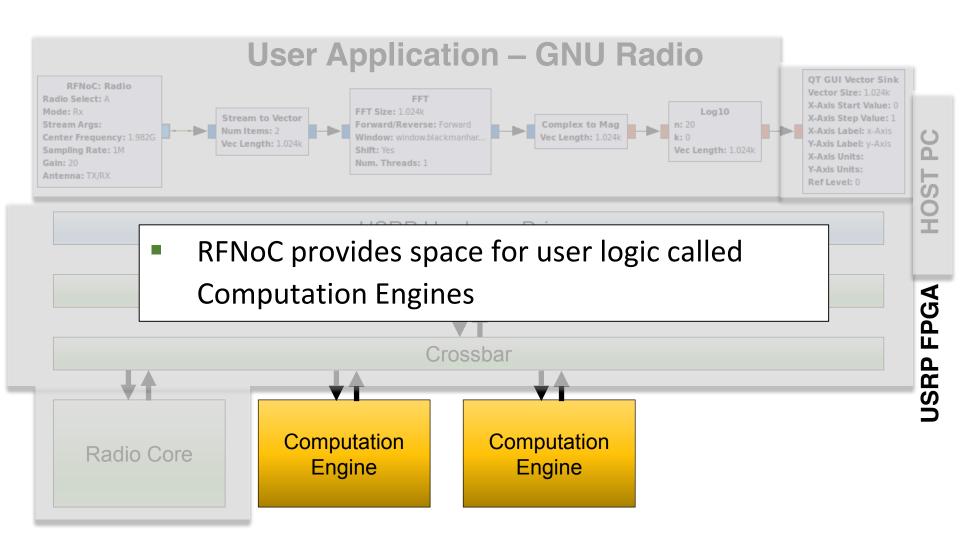

- User interfaces to RFNoC via AXI-Stream

- Industry standard (ARM), easy to use

- Large library of existing IP cores

**Ettus**

Ó

Researd

A National Instruments

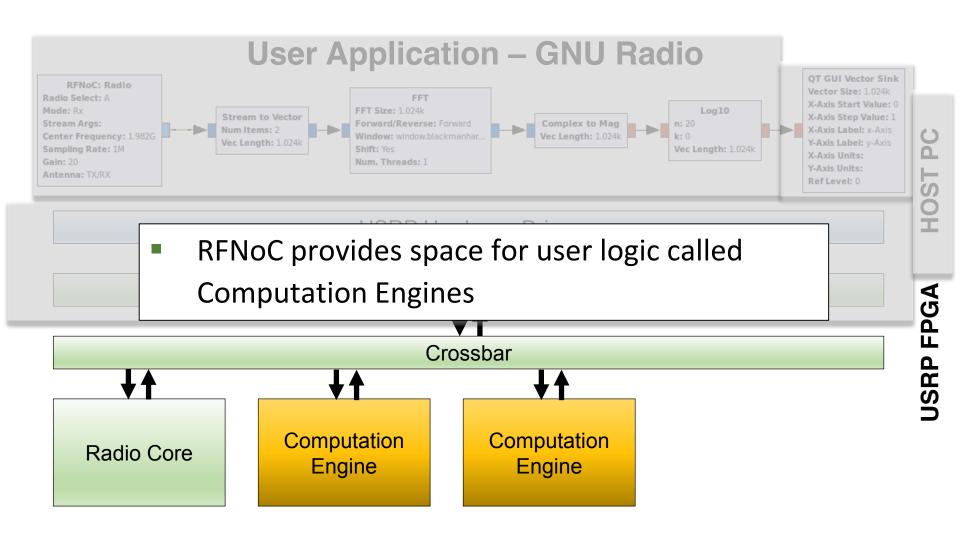

- User writes their own HDL or drops in IP

- Multiple AXI-Streams, Control / Status registers

**Ettus**

Resear

- Each block is in their own clock domain

- Improve block throughput, timing

- Interface to Crossbar has clock crossing FIFOs

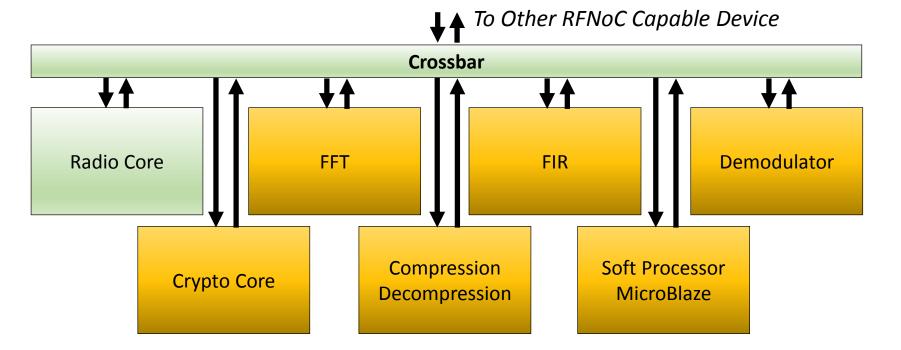

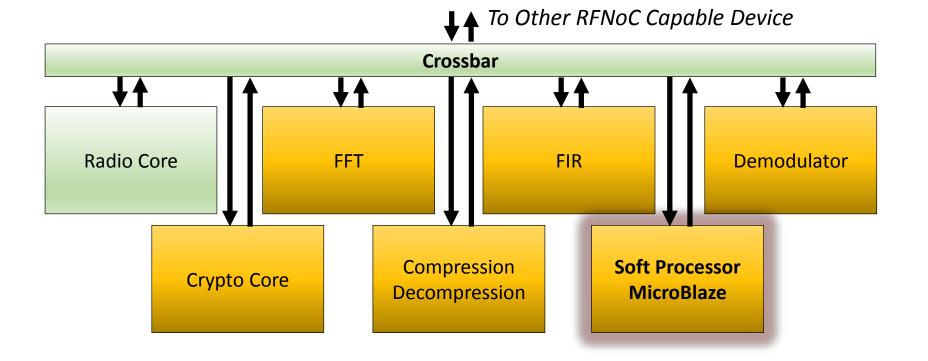

## **Many Types of CEs**

**Ettus**

0 4

- Many computation engines

- Not limited to one crossbar, one device

- Scales across devices for massive distributed processing

#### **Many Types of CEs**

**Ettus**

0 6 0

Researc

A National Instruments

#### Low latency protocol processing in FPGA

**Ettus**

**Ettus** Resear A National Instruments

Ó

**Ettus**

0 4

Research

A National Instruments Co

# DEMO

### Summary

Simple architecture for heterogeneous data flow processing

**Ettus**

- Implemented several interesting CEs

- Integrated with high level SDR framework

- Portable between all third generation USRPs

- X3x0, E310, and products soon to come

- Completely open source

- Beta release available!

- github.com/EttusResearch/uhd/wiki/RFNoC:-Getting-Started