Difference between revisions of "RFNoC (UHD 3.0)"

From Ettus Knowledge Base

(→Sample of Available Blocks) |

|||

| Line 36: | Line 36: | ||

*OFDM: Burst detection + synchronization, equalizer, packet demodulator | *OFDM: Burst detection + synchronization, equalizer, packet demodulator | ||

*and [https://github.com/EttusResearch/fpga/tree/maint/usrp3/lib/rfnoc more...] | *and [https://github.com/EttusResearch/fpga/tree/maint/usrp3/lib/rfnoc more...] | ||

| + | |||

| + | ==Blocks Included with Default FPGA Images== | ||

| + | The following images have the corresponding RFNoC blocks (Computation Engines): | ||

| + | |||

| + | {| class="wikitable" | ||

| + | !Image Name | ||

| + | !Included Blocks | ||

| + | |- | ||

| + | |||

| + | |<code>usrp_x300_fpga_HG.bit</code> | ||

| + | <code>usrp_x300_fpga_XG.bit</code> | ||

| + | |||

| + | <code>usrp_x310_fpga_HG.bit</code> | ||

| + | |||

| + | <code>usrp_x310_fpga_XG.bit</code> | ||

| + | |<code>2x DDC, 2x DUC</code> | ||

| + | |- | ||

| + | |||

| + | |<code>usrp_x300_fpga_RFNOC_HG.bit</code> | ||

| + | <code>usrp_x300_fpga_RFNOC_XG.bit</code> | ||

| + | |<code>DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs</code> | ||

| + | |- | ||

| + | |||

| + | |<code>usrp_x310_fpga_RFNOC_HG.bit</code> | ||

| + | <code>usrp_x310_fpga_RFNOC_XG.bit</code> | ||

| + | |<code>DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs, Keep One in N, FIR, Siggen</code> | ||

| + | |- | ||

| + | |||

| + | |<code>usrp_e310_fpga.bit</code> | ||

| + | <code>usrp_e310_fpga_sg3.bit</code> | ||

| + | |<code>1x DDC, 1x DUC</code> | ||

| + | |- | ||

| + | |||

| + | |<code>usrp_e310_fpga_RFNOC.bit (sg1 version)</code> | ||

| + | <code>usrp_e310_fpga_RFNOC_sg3.bit</code> | ||

| + | |<code>fosphor, window, fft, 2x AXI FIFOs, FIR</code> | ||

| + | |- | ||

| + | |||

| + | |} | ||

| + | |||

| + | |||

==RFNoC Resources== | ==RFNoC Resources== | ||

Revision as of 15:02, 17 January 2017

Contents

Overview

Framework and Data Flow Example

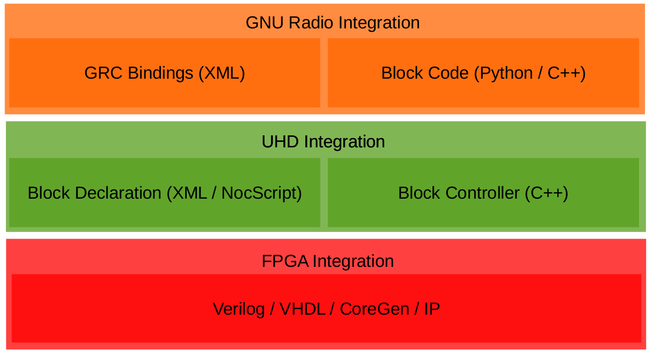

Below is a figure of the RFNoC stack.

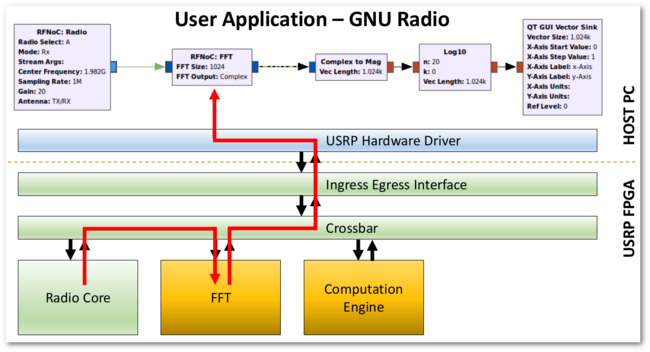

The example below shows basic data flow of an RFNoC application. While this shows one possible data flow, there are many possible combinations from Host block to FPGA block, FPGA block to Host block, Host to Host, FPGA to FPGA, etc.

Supported Devices

- E310/E312

- X300/X310

Sample of Available Blocks

- FIFO

- FFT

- FIR

- fosphor (real-time spectrum analyzer)

- Decimator (Keep 1 in N)

- Log Power Calculator

- Radio Interface

- Vector IIR (moving average)

- Window multiplier (for FFT)

- OFDM: Burst detection + synchronization, equalizer, packet demodulator

- and more...

Blocks Included with Default FPGA Images

The following images have the corresponding RFNoC blocks (Computation Engines):

| Image Name | Included Blocks |

|---|---|

usrp_x300_fpga_HG.bit

|

2x DDC, 2x DUC

|

usrp_x300_fpga_RFNOC_HG.bit

|

DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs

|

usrp_x310_fpga_RFNOC_HG.bit

|

DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs, Keep One in N, FIR, Siggen

|

usrp_e310_fpga.bit

|

1x DDC, 1x DUC

|

usrp_e310_fpga_RFNOC.bit (sg1 version)

|

fosphor, window, fft, 2x AXI FIFOs, FIR

|