Difference between revisions of "RFNoC (UHD 3.0)"

(added FAQ section and added FAQ under GR) |

|||

| Line 76: | Line 76: | ||

|} | |} | ||

| + | ==RFNoC FAQs== | ||

| + | ===FPGA=== | ||

| + | Coming soon... | ||

| + | ===UHD=== | ||

| + | Coming soon... | ||

| + | ===GNU Radio=== | ||

| + | ====When do I use an RFNoC FIFO in my flowgraph and which kind if any?==== | ||

| + | |||

| + | An RFNoC FIFO is needed in your flowgraph in the following 2 conditions: | ||

| + | |||

| + | First, if you are running a GNU Radio flowgraph that is structured as follows: | ||

| + | |||

| + | <code>Host block -> RFNoC block -> Host block</code> | ||

| + | |||

| + | In this case, you need to do either: | ||

| + | |||

| + | <code>Host block -> RFNoC FIFO -> RFNoC Block -> Host block</code> | ||

| + | |||

| + | -OR- | ||

| + | |||

| + | <code>Host block -> RFNoC Block -> RFNoC FIFO -> Host block</code> | ||

| + | |||

| + | The order doesn't matter. This structure also benefits from having the [http://gnuradio.org/redmine/projects/gnuradio/wiki/Guided_Tutorial_GRC#243-A-Note-on-the-Throttle-Block GNU Radio Throttle block] in the sequence.The reason behind the need to add the FIFO is because of performance inside of GNU Radio, so that the RX/TX work functions in the GNU Radio RFNoC block implementations run in separate threads. | ||

| + | |||

| + | Use '''RFNoC: FIFO''' (AXI_FIFO_LOOPBACK) in this case. See the following figure as an example. | ||

| + | |||

| + | [[File:fifo_v01.png|650px]] | ||

| + | |||

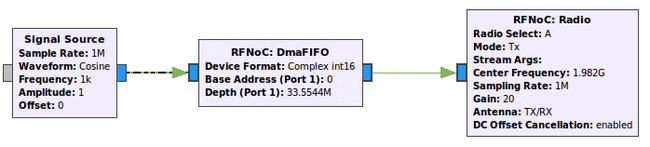

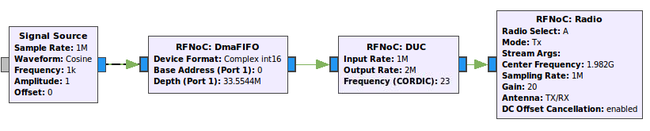

| + | Second, in the case where you are transmitting out to the antenna on the X3xx series devices, i.e. | ||

| + | |||

| + | <code>Host -> DmaFIFO -> Radio</code> | ||

| + | |||

| + | -OR- | ||

| + | |||

| + | <code>Host -> DmaFIFO -> DUC -> Radio</code> | ||

| + | |||

| + | Ethernet introduces a latency in flow control from the X3x0 back to the host. The latency will cause underruns unless a large buffer, i.e. DMA_FIFO, is added to the flowgraph. | ||

| + | |||

| + | Use '''RFNoC: DmaFIFO''' (AXI_DMA_FIFO) in this case. See the following figures as examples. | ||

| + | |||

| + | [[File:dma_fifo_v01.png|650px]] | ||

| + | |||

| + | -OR- | ||

| + | |||

| + | [[File:dma_fifo_v02.png|650px]] | ||

Revision as of 00:26, 29 January 2017

Contents

Overview

Framework and Data Flow Example

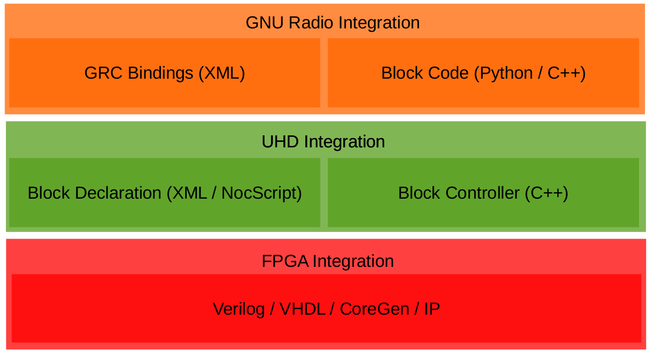

Below is a figure of the RFNoC stack.

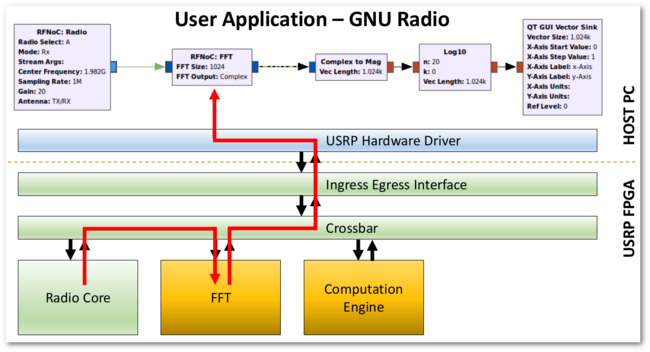

The example below shows basic data flow of an RFNoC application. While this shows one possible data flow, there are many possible combinations from Host block to FPGA block, FPGA block to Host block, Host to Host, FPGA to FPGA, etc.

Supported Devices

- E310/E312

- X300/X310

Sample of Available Blocks

- FIFO

- FFT

- FIR

- fosphor (real-time spectrum analyzer)

- Decimator (Keep 1 in N)

- Log Power Calculator

- Radio Interface

- Vector IIR (moving average)

- Window multiplier (for FFT)

- OFDM: Burst detection + synchronization, equalizer, packet demodulator

- and more...

Blocks Included with Default FPGA Images

The following images have the corresponding RFNoC blocks (Computation Engines):

| Image Name | Included Blocks |

|---|---|

usrp_x300_fpga_HG.bit

|

2x DDC, 2x DUC

|

usrp_x300_fpga_RFNOC_HG.bit

|

DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs

|

usrp_x310_fpga_RFNOC_HG.bit

|

DUC, DDC (one channel), fosphor, window, fft, 2x AXI FIFOs, Keep One in N, FIR, Siggen

|

usrp_e310_fpga.bit

|

1x DDC, 1x DUC

|

usrp_e310_fpga_RFNOC.bit (sg1 version)

|

fosphor, window, fft, 2x AXI FIFOs, FIR

|

RFNoC FAQs

FPGA

Coming soon...

UHD

Coming soon...

GNU Radio

When do I use an RFNoC FIFO in my flowgraph and which kind if any?

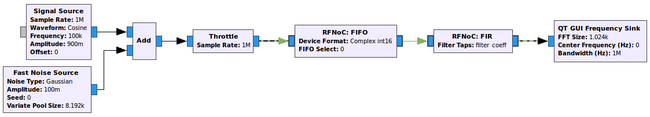

An RFNoC FIFO is needed in your flowgraph in the following 2 conditions:

First, if you are running a GNU Radio flowgraph that is structured as follows:

Host block -> RFNoC block -> Host block

In this case, you need to do either:

Host block -> RFNoC FIFO -> RFNoC Block -> Host block

-OR-

Host block -> RFNoC Block -> RFNoC FIFO -> Host block

The order doesn't matter. This structure also benefits from having the GNU Radio Throttle block in the sequence.The reason behind the need to add the FIFO is because of performance inside of GNU Radio, so that the RX/TX work functions in the GNU Radio RFNoC block implementations run in separate threads.

Use RFNoC: FIFO (AXI_FIFO_LOOPBACK) in this case. See the following figure as an example.

Second, in the case where you are transmitting out to the antenna on the X3xx series devices, i.e.

Host -> DmaFIFO -> Radio

-OR-

Host -> DmaFIFO -> DUC -> Radio

Ethernet introduces a latency in flow control from the X3x0 back to the host. The latency will cause underruns unless a large buffer, i.e. DMA_FIFO, is added to the flowgraph.

Use RFNoC: DmaFIFO (AXI_DMA_FIFO) in this case. See the following figures as examples.

-OR-