Difference between revisions of "E310/E312"

From Ettus Knowledge Base

(→Interfaces and Connectivity) |

(→Interfaces and Connectivity) |

||

| Line 405: | Line 405: | ||

*Host USB support | *Host USB support | ||

*9-axis IMU | *9-axis IMU | ||

| + | |||

| + | |||

| + | ===GPIO=== | ||

| + | {| | ||

| + | |||

| + | | style="width:60%" | | ||

| + | '''Pin Mapping''' | ||

| + | * Pin 1: +3.3V | ||

| + | * Pin 2: Reserved | ||

| + | * Pin 3: Data[5] | ||

| + | * Pin 4: Reserved | ||

| + | * Pin 5: Data[4] | ||

| + | * Pin 6: Data[0] | ||

| + | * Pin 7: Data[3] | ||

| + | * Pin 8: Data[1] | ||

| + | * Pin 9: 0V | ||

| + | * Pin 10: Data[2] | ||

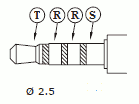

| + | |[[File:e3x0 gpio conn.png]] | ||

| + | |} | ||

| + | * Please see the [http://files.ettus.com/manual/page_gpio_api.html E3x0/X3x0 GPIO API] for information on configuring and using the GPIO bus. | ||

===Audio=== | ===Audio=== | ||

Revision as of 14:35, 24 May 2016

Contents

Device Overview

The USRP E310 offers a portable stand-alone SDR platform designed for field deployment. The flexible 2x2 MIMO AD9361 transceiver from Analog Devices provides up to 56 MHz of instantaneous bandwidth and spans frequencies from 70 MHz – 6 GHz to cover multiple bands of interest.

Key Features

E310

|

E312

|

RF Specifications

RF Performance

- SSB/LO Suppression -35/50 dBc

- Phase Noise 3.5 GHz 1.0 deg RMS

- Phase Noise 6 GHz 1.5 deg RMS

- Power Output >10dBm

- IIP3 (@ typ NF) -20dBm

- Typical Noise Figure <8dB

Hardware Specifications

- Ettus Research recommends to always use the latest stable version of UHD

E310

- Current Hardware Revision: 1

- Minimum version of UHD required: 3.8.0

- Required version on the host computer must match what is running on the E310

E312

- Current Hardware Revision: 1

- Minimum version of UHD required: 3.8.5

- Required version on the host computer must match what is running on the E312

Physical Specifications

Dimensions

- 133 x 68 x 26.4 mm

Environmental Specifications

Operating Temperature Range

- E310 0-40 °C

Schematics

E310

Key Component Datasheets

| Part Number | Description | Schematic ID (Page) |

|---|---|---|

| Motherboard | ||

| TXS02612RTWR | SDIO PORT EXPANDER | U23 (2) |

| XC7Z020-1CLG484CES9919 | FPGA | U11 (2,3,4,8,11,13) |

| Xilinx Zynq Product Page | FPGA | - |

| USB3340-EZK-TR | ULPI Transceiver | U33 (5) |

| AK4571VQP | Audio CODEC | U30 (6) |

| FT230XQ-R | UART Interface | U32 (6) |

| 88E1512 | Gigabit Ethernet Transceiver | U13 (7) |

| 24LC024/SN | EEPROM | U5 (9) |

| DS1339,SM | Real-Time Clock | U6 (9) |

| ADT7408 | Temperature Sensor | U8 (9) |

| MPU-9150 | Motion Processing Unit | U3 (9) |

| InvenSense MPU-9150 Product Page | Motion Processing Unit | U3 (9) |

| BMP180 | Digital pressure sensor | U4 (9) |

| BQ24192 | Adapter Charger | U1 (10) |

| TPS54478 | Step-Down Switcher | U20 (10) |

| MAX6510HAUT-T | Temperature Switches | U35 (10) |

| ATTINY88-MU | Microcontroller | U18 (10) |

| TPS61253YFF | Step-Up Converter | U19 (10) |

| Daughterboard | ||

| Part Number | Description | Schematic ID (Page) |

| AD9361 Product Page | 2 x 2 RF Agile Transceiver | U8 (3) |

| 24AA256 | EEPROM | U15 (2) |

| TC-1-43A+ | RF Transformer | T6 (3); T5 (3); T4 (3) |

| TC1-1-13M+ | RF Transformer | T7 (3); T10 (3); T1 (3) |

| TPS62140 | Step-Down Converter | U19 (4) |

| ADP1753ACPZ-R7 | Linear Regulator | U17 (4); U18 (4) |

| SGA-4563Z | MMIC AMPLIFIER | U12 (5); U4 (5) |

| SKY13418-485LF | Antenna Switch | U13 (5); U3 (5); U16 (5); U2 (5); U10 (6); U5 (6) |

| SKY13373-460LF | SP3T Switch | U11 (6); U9 (6); U6 (6); U7 (6); SW4 (7); SW1 (7) |

| MGA-81563 | Amplifier | U14 (5); U1 (5) |

| LFCN-5850+ | Low Pass Filter | FL32 (5); FL1 (5) |

| LFCN-2750+ | Low Pass Filter | FL37 (5); FL4 (5) |

| LFCN-2250+ | Low Pass Filter | FL23 (6); FL20 (6) |

| LFCN-1700+ | Low Pass Filter | FL40 (5); FL2 (5) |

| LFCN-1575+ | Low Pass Filter | FL25 (6); FL17 (6) |

| LFCN-1000+ | Low Pass Filter | FL33 (5); FL9 (5); FL27 (6); FL15 (6) |

| LFCN-575+ | Low Pass Filter | FL36 (5); FL5 (5) |

| LFCN-530+ | Low Pass Filter | FL29 (6); FL13 (6) |

| LFCN-400+ | Low Pass Filter | FL38 (5); FL3 (5); FL30 (6); FL11 (6) |

| LFCN-225 | Low Pass Filter | FL39 (5); FL6 (5) |

| LFCN-160+ | Low Pass Filter | FL34 (5); FL8 (5) |

| LFCN-80+ | Low Pass Filter | FL35 (5); FL7 (5) |

| HFCN-1600+ | High Pass Filter | FL22 (6); FL19 (6) |

| HFCN-1100+ | High Pass Filter | FL24 (6); FL16 (6) |

| HFCN-650+ | High Pass Filter | FL26 (6); FL14 (6) |

| HFCN-440+ | High Pass Filter | FL28 (6); FL12 (6) |

| BFCN-2435+ | Bandpass Filter | FL21 (6); FL18 (6) |

| FDG6301N | Dual N-Channel, Digital FET | Q8 (7); Q5 (7) |

| HSMS-8202 | Mixer Diodes | CR1 (7); CR2 (7); CR3 (7); CR4 (7) |

| LP5900TL | Linear Regulator | U25 (8) |

| ADP150AUJZ-3.0 | Linear Regulator | U22 (8) |

| AD5662RBJ | 16-Bit nanoDAC | U21 (8) |

| SN74AUP1T57 | Voltage Translator | U27 (8); U28 (8); U29 (8) |

Request a detailed whitepaper covering features and components from [email protected]

Mechanical Information

Weight

- Partial Enclosure 225 g

- Full Enclosure 375 g

Drawings

- E310 Drawings - File:E310 Dimensional Sketches.pdf

FPGA

- Utilization statistics are subject to change between UHD releases, current as of UHD 3.9.4

E310/E312

1. Slice Logic -------------- +----------------------------+-------+-----------+-------+ | Site Type | Used | Available | Util% | +----------------------------+-------+-----------+-------+ | Slice LUTs | 36203 | 53200 | 68.05 | | LUT as Logic | 28108 | 53200 | 52.83 | | LUT as Memory | 8095 | 17400 | 46.52 | | LUT as Distributed RAM | 870 | | | | LUT as Shift Register | 7225 | | | | Slice Registers | 36562 | 106400 | 34.36 | | Register as Flip Flop | 36562 | 106400 | 34.36 | | Register as Latch | 0 | 106400 | 0.00 | | F7 Muxes | 376 | 26600 | 1.41 | | F8 Muxes | 125 | 13300 | 0.93 | +----------------------------+-------+-----------+-------+ 3. Memory --------- +-------------------+------+-----------+-------+ | Site Type | Used | Available | Util% | +-------------------+------+-----------+-------+ | Block RAM Tile | 97 | 140 | 69.28 | | RAMB36/FIFO* | 90 | 140 | 64.28 | | RAMB36E1 only | 90 | | | | RAMB18 | 14 | 280 | 5.00 | | RAMB18E1 only | 14 | | | +-------------------+------+-----------+-------+ * Note: Each Block RAM Tile only has one FIFO logic available and therefore can accommodate only one FIFO36E1 or one FIFO18E1. However, if a FIFO18E1 occupies a Block RAM Tile, that tile can still accommodate a RAMB18E1 4. DSP ------ +----------------+------+-----------+-------+ | Site Type | Used | Available | Util% | +----------------+------+-----------+-------+ | DSPs | 120 | 220 | 54.54 | | DSP48E1 only | 120 | | | +----------------+------+-----------+-------+

Interfaces and Connectivity

- 10/100/1000 BASE-T Ethernet

- Stereo audio out, mono mic in

- Integrated GPS receiver

- Host USB support

- 9-axis IMU

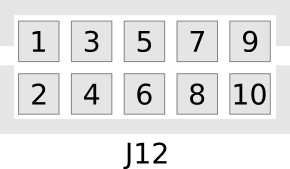

GPIO

|

Pin Mapping

|

|

- Please see the E3x0/X3x0 GPIO API for information on configuring and using the GPIO bus.

Audio

Certifications

RoHS

As of December 1st, 2010 all Ettus Research products are RoHS compliant unless otherwise noted. More information can be found at http://ettus.com/legal/rohs-information